SENIOR DESIGN

# SECURITY OF ELECTRONIC SAFETY LOCKS PROJECT SPECIFICATION DOCUMENT - GROUP 3

Neal Gardella Ryan Ostroff Connor Owen Russell Owen

May 15, 2023

# Contents

| 1 | Overv  | riew                                                                 | 6 |

|---|--------|----------------------------------------------------------------------|---|

|   | 1.1    | Executive Summary                                                    | 6 |

|   | 1.2    | Team contact information and protocols                               | 7 |

|   |        | 1.2.1 Expected Contributions                                         | 7 |

|   |        | 1.2.2 Team Protocols                                                 | 7 |

|   |        | 1.2.3 Project Sponsor Communication and Collaboration Preferences: 8 | 8 |

|   | 1.3    | Gap Analysis                                                         | 9 |

|   | 1.4    | Proposed Timeline                                                    | 9 |

|   | 1.5    | References and File Links                                            | 0 |

|   |        | 1.5.1 References                                                     | 0 |

|   |        | 1.5.2 File Links                                                     | 0 |

|   | 1.6    | Revision Table                                                       | 0 |

| 2 | Impac  | ts and Risks                                                         | 1 |

|   | 2.1    | Design Impact Statement 1                                            | 1 |

|   | 2.2    | Risks 12                                                             | 2 |

|   | 2.3    | References and File Links                                            | 2 |

|   |        | 2.3.1 References                                                     | 2 |

|   |        | 2.3.2 File Links                                                     | 3 |

|   | 2.4    | Revision Table                                                       | 4 |

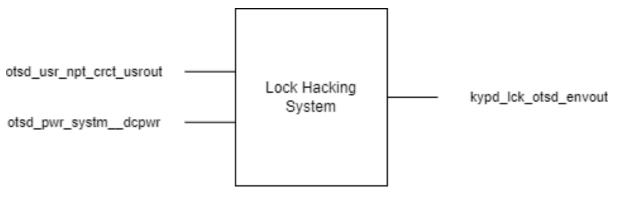

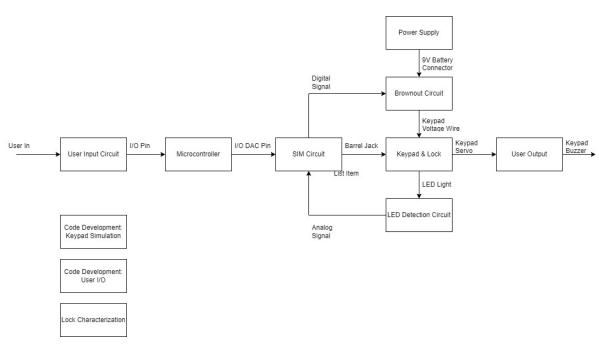

| 3 | Top Le | evel Architecture                                                    | 4 |

|   | 3.1    | Block Diagram                                                        | 4 |

|   | 3.2    | Block Descriptions 15                                                | 5 |

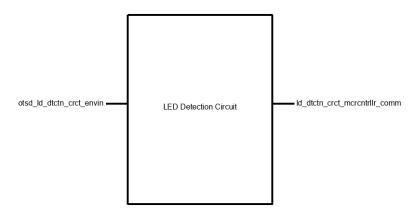

|   |        | 3.2.1 LED Detection Circuit                                          | 5 |

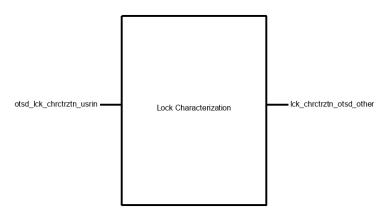

|   |        | 3.2.2 Lock Characterization                                          | 5 |

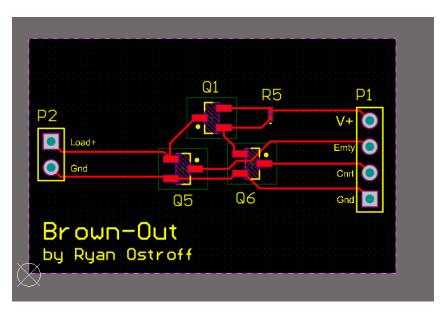

|   |        | 3.2.3 Brown-Out Circuit                                              | 5 |

|   |        | 3.2.4 Power System                                                   | 6 |

|   |        | 3.2.5 Code Development I/O                                           | 6 |

|   |        | 3.2.6 Microcontroller                                                | 6 |

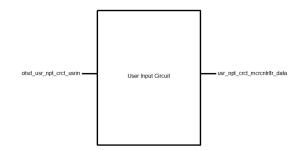

|   |        | 3.2.7 User Input Circuit                                             | 6 |

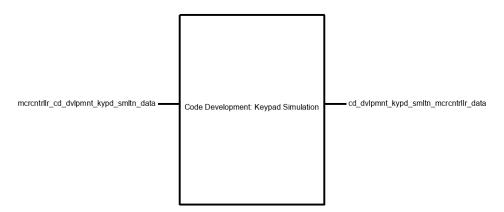

|   |        | 3.2.8 Code Development: Keypad Simulation                            | 7 |

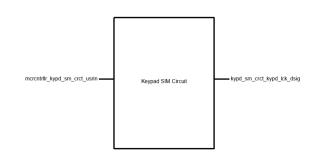

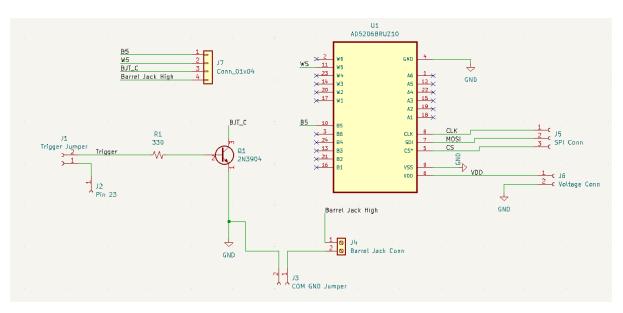

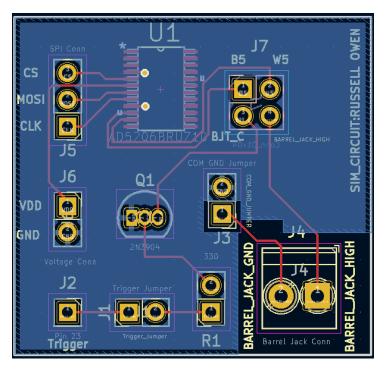

|   |       | 3.2.9      | Keypad SIM Circuit        | 17 |

|---|-------|------------|---------------------------|----|

|   |       | 3.2.10     | Keypad Lock               | 17 |

|   | 3.3   | Interface  | e Definitions             | 18 |

|   | 3.4   | Referen    | ces and File Links        | 19 |

|   |       | 3.4.1      | References                | 19 |

|   |       | 3.4.2      | File Links                | 19 |

|   | 3.5   | Revision   | 1 Table                   | 19 |

| 4 | Block | Validatior | IS                        | 19 |

|   | 4.1   | Lock Ch    | aracterization            | 19 |

|   |       | 4.1.1      | Description               | 19 |

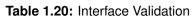

|   |       | 4.1.2      | Design                    | 20 |

|   |       | 4.1.3      | General Validation        | 21 |

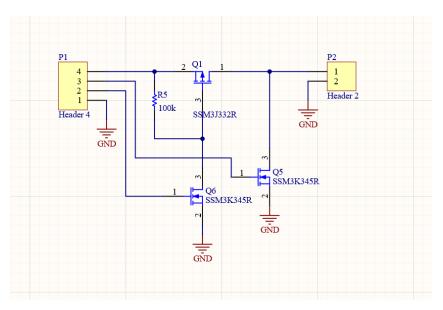

|   |       | 4.1.4      | Interface Validation      | 21 |

|   |       | 4.1.5      | Verification Process      | 21 |

|   |       | 4.1.6      | References and File Links | 23 |

|   |       | 4.1.7      | Revision Table            | 23 |

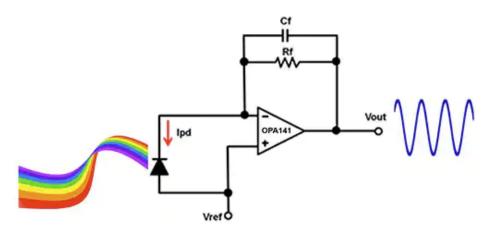

|   | 4.2   | LED Det    | tection Circuit           | 23 |

|   |       | 4.2.1      | Description               | 23 |

|   |       | 4.2.2      | Design                    | 24 |

|   |       | 4.2.3      | General Validation        | 24 |

|   |       | 4.2.4      | Interface Validation      | 24 |

|   |       | 4.2.5      | Verification Process      | 24 |

|   |       | 4.2.6      | References and File Links | 25 |

|   |       | 4.2.7      | Revision Table            | 25 |

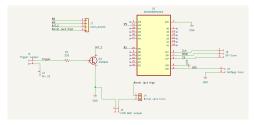

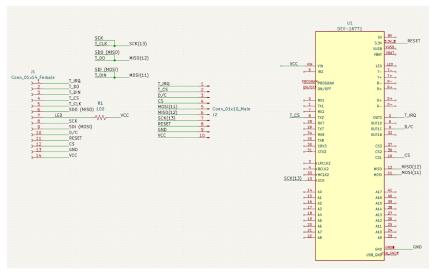

|   | 4.3   | Keypad     | SIM Circuit               | 25 |

|   |       | 4.3.1      | Description               | 25 |

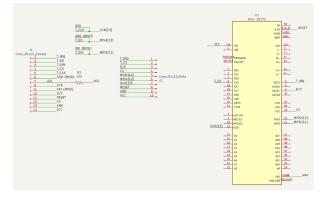

|   |       | 4.3.2      | Design                    | 25 |

|   |       | 4.3.3      | General Validation        | 26 |

|   |       | 4.3.4      | Interface Validation      | 28 |

|   |       | 4.3.5      | Verification Process      | 29 |

|   |       | 4.3.6      | References and File Links | 30 |

|   |       | 4.3.7      | Revision Table            | 30 |

|   | 4.4   | Keypad     | SIM Code                  | 30 |

|   |       | 4.4.1      | Description               | 30 |

|   |       | 4.4.2      | Design                    | 31 |

|   | 4.5   | User Inp   | out Circuit               | 31 |

|   |       | 4.5.1      | Description               | 31 |

|   |       | 4.5.2      | Design                    | 32 |

5

|        | 4.5.3       | General Validation                                    | 32 |

|--------|-------------|-------------------------------------------------------|----|

|        | 4.5.4       | Interface Validation                                  | 35 |

|        | 4.5.5       | Verification Process                                  | 36 |

|        | 4.5.6       | References and File Links                             | 37 |

|        | 4.5.7       | Revision Table                                        | 37 |

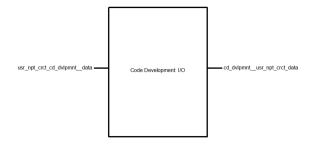

| 4.6    | User I/O    | Code                                                  | 37 |

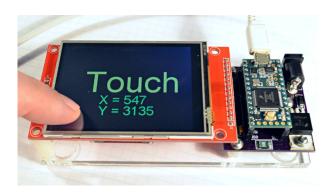

|        | 4.6.1       | Description                                           | 37 |

|        | 4.6.2       | Design                                                | 37 |

|        | 4.6.3       | General Validation                                    | 38 |

|        | 4.6.4       | Interface Validation                                  | 38 |

|        | 4.6.5       | Verification Process                                  | 38 |

|        | 4.6.6       | References and File Links                             | 39 |

|        | R           | eferences                                             | 39 |

|        | Fi          | le Links                                              | 39 |

|        | 4.6.7       | Revision Table                                        | 39 |

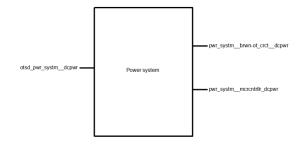

| 4.7    | Power S     | ystem                                                 | 39 |

|        | 4.7.1       | Description                                           | 39 |

|        | 4.7.2       | Design                                                | 39 |

|        | 4.7.3       | General Validation                                    | 40 |

|        | 4.7.4       | Interface Validation                                  | 40 |

|        | 4.7.5       | Verification Process                                  | 41 |

|        | 4.7.6       | References and File Links                             | 41 |

|        | R           | eferences                                             | 41 |

|        | 4.7.7       | Revision Table                                        | 41 |

| 4.8    | Brown-o     | ut Circuit                                            | 42 |

|        | 4.8.1       | Description                                           | 42 |

|        | 4.8.2       | Design                                                | 42 |

|        | 4.8.3       | General Validation                                    | 44 |

|        | 4.8.4       | Interface Validation                                  | 44 |

|        | 4.8.5       | Verification Process                                  | 45 |

|        | 4.8.6       | References and File Links                             | 45 |

|        | R           | eferences                                             | 45 |

|        | 4.8.7       | Revision Table                                        | 46 |

| Syster | n Verificat | tion Evidence                                         | 46 |

| 5.1    | Universa    | Il Constraints                                        | 46 |

|        | 5.1.1       | The system may not include a breadboard               | 46 |

|        | 5.1.2       | All connections to PCBs must use connectors:          | 46 |

|        | 5.1.3       | The final system must contain a student-designed PCB: | 46 |

|     | 5.1.4 | All pow    | er supplies in the system must be at least 65% efficient: | 47 |

|-----|-------|------------|-----------------------------------------------------------|----|

|     | 5.1.5 | The sy     | stem may be no more than 50% built from purchased         |    |

|     |       | 'module    | es':                                                      | 47 |

| 5.2 | Requi | irements . |                                                           | 47 |

|     | 5.2.1 | Code D     | Development: I/O Functionality                            | 47 |

|     |       | 5.2.1.1    | Project Partner Requirement:                              | 47 |

|     |       | 5.2.1.2    | Engineering Requirement:                                  | 47 |

|     |       | 5.2.1.3    | Verification Process:                                     | 47 |

|     |       | 5.2.1.4    | Testing Evidence:                                         | 48 |

|     | 5.2.2 | Seamle     | ess Connection to Keypad and Lock                         | 48 |

|     |       | 5.2.2.1    | Project Partner Requirement:                              | 48 |

|     |       | 5.2.2.2    | Engineering Requirement:                                  | 48 |

|     |       | 5.2.2.3    | Verification Process:                                     | 48 |

|     |       | 5.2.2.4    | Testing Evidence:                                         | 48 |

|     | 5.2.3 | Automa     | ated Hacking Process                                      | 48 |

|     |       | 5.2.3.1    | Project Partner Requirement:                              | 48 |

|     |       | 5.2.3.2    | Engineering Requirement:                                  | 48 |

|     |       | 5.2.3.3    | Verification Process:                                     | 49 |

|     |       | 5.2.3.4    | Testing Evidence:                                         | 49 |

|     | 5.2.4 | Powers     | system                                                    | 49 |

|     |       | 5.2.4.1    | Project Partner Requirement:                              | 49 |

|     |       | 5.2.4.2    | Engineering Requirement:                                  | 49 |

|     |       | 5.2.4.3    | Verification Process:                                     | 49 |

|     |       | 5.2.4.4    | Testing Evidence:                                         | 49 |

|     | 5.2.5 | Brown-     | out control                                               | 49 |

|     |       | 5.2.5.1    | Project Partner Requirement:                              | 49 |

|     |       | 5.2.5.2    | Engineering Requirement:                                  | 49 |

|     |       | 5.2.5.3    | Verification Process:                                     | 49 |

|     |       | 5.2.5.4    | Testing Evidence:                                         | 49 |

|     | 5.2.6 | Usabilit   | ty                                                        | 49 |

|     |       | 5.2.6.1    | Project Partner Requirement:                              | 49 |

|     |       | 5.2.6.2    | Engineering Requirement:                                  | 50 |

|     |       | 5.2.6.3    | Verification Process:                                     | 50 |

|     |       | 5.2.6.4    | Testing Evidence:                                         | 50 |

|     | 5.2.7 | Lock C     | haracterization                                           | 50 |

|     |       | 5.2.7.1    | Project Partner Requirement:                              | 50 |

|     |       | 5.2.7.2    | Engineering Requirement:                                  | 50 |

|     |       | 5.2.7.3    | Verification Process:                                     | 50 |

|     |       |            |                                                           |    |

|   |        | 5         | .2.7.4      | Testing Evidence:            | 51 |

|---|--------|-----------|-------------|------------------------------|----|

|   |        | 5.2.8     | Success     | ful Lock Hacking             | 51 |

|   |        | 5         | .2.8.1      | Project Partner Requirement: | 51 |

|   |        | 5         | .2.8.2      | Engineering Requirement:     | 51 |

|   |        | 5         | .2.8.3      | Verification Process:        | 51 |

|   |        | 5         | .2.8.4      | Testing Evidence:            | 52 |

|   | 5.3    | Referen   | ces and F   | ile Links                    | 52 |

|   |        | 5.3.1     | Referen     | ces                          | 52 |

|   |        | 5.3.2     | File Link   | s                            | 52 |

|   | 5.4    | Revision  | Table .     |                              | 52 |

| 6 | Projec | t Closing |             |                              | 53 |

|   | 6.1    | Future F  | Recomme     | ndations                     | 53 |

|   |        | 6.1.1     | Technica    | al Recommendations           | 53 |

|   |        | 6.1.2     | Global II   | mpact Recommendation         | 54 |

|   |        | 6.1.3     | Teamwo      | rk Recommendation            | 54 |

|   | 6.2    | Project A | Artifact Su | ummary with Links            | 56 |

|   | 6.3    | Presenta  | ation Mate  | erials                       | 59 |

|   |        |           |             |                              |    |

## **1** Overview

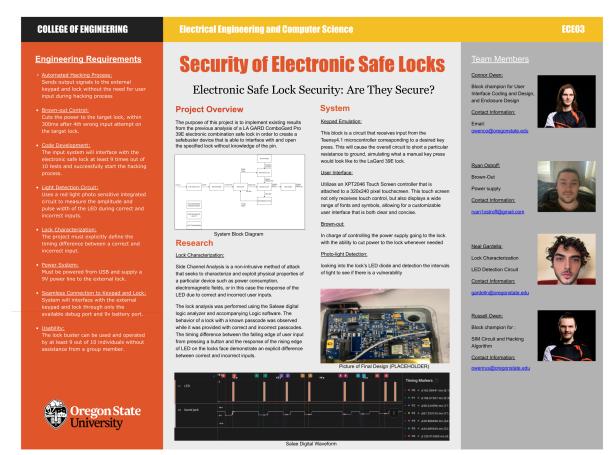

#### 1.1 Executive Summary

The purpose of this project is to implement existing results from the previous analysis of a LA GARD ComboGard Pro 39E electronic combination safe lock in order to create a safebuster device that is able to interface with and open the specified lock without knowledge of the pin. The current state of the project is in the analysis phase where as a team we are analyzing the lock in order to find additional vulnerabilities that can be used to create the safebuster device or support the current analysis that has already been given. The tools used for the analysis are a Saleae logic analyzer which scans the digital and analog channels on the internal PCB of the lock and a soldering station for attaching test points. Goals completed during this time were the successful attachment and test analysis of the logic analyzer as well as investigating potential micro-controllers for use in cracking the lock.

## 1.2 Team contact information and protocols

| Name          | Email                    |

|---------------|--------------------------|

| Neal Gardella | gardelln@oregonstate.edu |

| Ryan Ostroff  | ostroffr@oregonstate.edu |

| Connor Owen   | owenco@oregonstate.edu   |

| Russell Owen  | owenrus@oregonstate.edu  |

Table 1.1: Contact Information

| 1.2.1 Expected | Contributions |

|----------------|---------------|

|----------------|---------------|

| Name          | Role                                     | Expected Contributions                         |

|---------------|------------------------------------------|------------------------------------------------|

|               |                                          | Research timing attacks.                       |

| Neal Gardella | Research and design of electronics.      | Breadboard development.                        |

|               |                                          | Test analysis methods.                         |

|               |                                          | Research circuit architecture vulnerabilities, |

| Ryan Ostroff  | Research and design of PCB.              | Research possible components.                  |

| nyan Ostion   | Research and design of FCB.              | Test analysis methods.                         |

|               |                                          | PCB design and fab.                            |

|               | Research and design of microcontrollers. | Research power/side channel analysis.          |

| Connor Owen   |                                          | Microcontroller platform.                      |

| Connor Owen   |                                          | Code the microcontroller.                      |

|               |                                          | Test analysis methods.                         |

|               |                                          | Research motor control vulnerabilities         |

| Duesell Owen  | Descent and desire of mismore duality    | Research possible components.                  |

| Russell Owen  | Research and design of microcontrollers. | Code the microcontroller.                      |

|               |                                          | Test analysis methods.                         |

Table 1.2: Expected Contributions

#### 1.2.2 Team Protocols

Listed below are the agreed upon team protocols for work quality and communication.

#### Senior Design

| Торіс                            | Protocol                                                                                                                                                                                                             | Standard                                                                                                                                                                                                                          |

|----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| On time Deliverables and Tasks   | Drafts of all individuals' contributions to teamwork<br>submissions should be fully complete by the deadline<br>as outlined in the tasklist such that as a team we<br>may review them during our scheduled meetings. | Work submitted as complete will include all necessary content and formatting requirements listed in the ECE44X canvas and error free.                                                                                             |

| Task management and Organization | The team will use the shared Google Drive for<br>all of their organization of files and will use<br>the Task List within the drive to track their<br>record of completion                                            | During team meetings, the team will review<br>the tasks to be completed and assign out parts<br>to individuals. When a task is complete, it<br>should be marked green so that the team<br>can review during the next meeting.     |

| Team Communication               | The team will treat every other team member<br>with respect and will try to resolve matters in<br>a civil manner.                                                                                                    | During team meetings or during individual lab<br>working time, team members will carry<br>themselves cordially and civilly.                                                                                                       |

| Reaching Out for Help            | The team member will reach out for help on<br>a given task before the given deadline if they<br>cannot complete the task.                                                                                            | During any lab time or meeting a team member<br>should reach out for help with their given task<br>if they cannot complete it before the deadline<br>by formally asking another individual<br>team member over text or in person. |

#### 1.2.3 Project Sponsor Communication and Collaboration Preferences:

- 1. Project Partners' Interest: Vincent Immler is very interested in the project and would like to contribute in any way possible, through providing equipment to training team members on how to use certain solder stations. Their main role appears to be more hands on and supportive than other project partners in the past.

- 2. Project Partners' profession: Vincent Immler is a professor for the Oregon State University school of Electrical Engineering and Computer Science.

- 3. Main Information: Immler is looking to get to know vulnerabilities within a certain set of locks, some of which are already publicly available and some which are private. This is so he can build better analysis and safe cracking methods. Immler also would like to know the solution to opening some of these locks so we as a team can create a safe cracking method that is efficient and universal.

- 4. Technical Knowledge: Vincent Immler knows a great amount about security vulnerabilities as his area of research and previous work is in the field. He knows the protocols that are used within the locks as well as the types of attacks that can be used to open them.

- 5. Preferred format and Frequency of Communication: We as a team have been instructed to check in with Immler through email every two weeks and when we have any questions about the project. We may also meet in person or in the Analog Mix Signal Laboratory if we need help beyond that of an email such as soldering or using equipment.

- 6. Other Individuals: There aren't any others who our Project Sponsor has shown various types of communications to during our initial meeting.

#### 1.3 Gap Analysis

Electronic safe locks are becoming more convenient when compared to mechanical locks but many designs suffer from vulnerabilities that make them prone to timing side-channel analysis, voltage glitching, and lockout-defeat strategies. Since electronic locks are widely used to store valuables, their security is the most important feature. This project looks to take one lock and use the methods stated previously to expose vulnerabilities in the lock to allow manufacturers to make design improvements to improve the security of their locks.

This project will fulfill the need to better characterize lock vulnerabilities based on a manufacturer's particular architecture. It also aims to automate the electronic lock-picking process to better show the repeatability of the vulnerabilities.

When meeting with the project partner, and conducting research through professional communities such as the DEFCON Conference, the needs that are fulfilled by the project are to improve the security of electronic locks through analysis, reverse engineering of lock architecture, and electronic attacks to expose the vulnerabilities of the locks which is relayed back to the manufacturer so that changes can be made.

The end user of electronic locks is the everyday person. Many people use electronic locks to store valuables like jewelry, money, and documents such as passports, and birth certificates. These end users rely on their safe to protect their valuables in the event of burglary or theft so the more secure the safe, the better an experience for that end user. Outside of the end users, the lock manufacturers are significant stakeholders as any improvements on existing electronic lock models will result in a higher quality product.

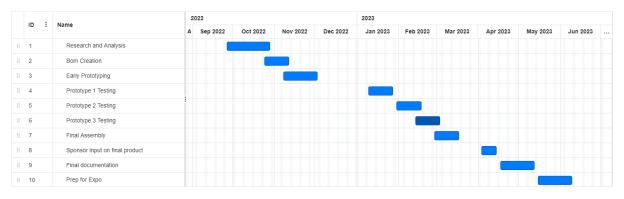

#### 1.4 Proposed Timeline

Figure 1.1: Proposed Timeline

#### 1.5 References and File Links

#### 1.5.1 References

- DEFCONConference, "DEF CON 24 plore side channel attacks on High Security Electronic Safe Locks," YouTube, 10-Nov-2016. [Online]. Available: https://www.youtube.com/wa tch?v=IXFpCV646E0. [Accessed: 16-Nov-2022].

- 2. "EECS Project Portal," EECS Project Submission Form | OSU. [Online]. Available: https://eecs.oregonstate.edu/capstone/submission/pages/. [Accessed: 16-Nov-2022].

#### 1.5.2 File Links

1. https://drive.google.com/drive/folders/1tpi62i4hFNSUOOfPLSZII8ekPSLUHxg-? usp=sharing

#### 1.6 Revision Table

| Date       | Name and Update                                                    |

|------------|--------------------------------------------------------------------|

|            | Connor Owen: Initial content for team contact                      |

| 10/10/2022 | information and protocols, and initial content                     |

|            | for the executive summary.                                         |

| 10/10/2022 | Russell Owen: Added gap analysis section                           |

| 10/10/22   | Ryan Ostroff: Created online gantt chart                           |

| 10/31/22   | Connor Owen: Updated executive summary with additional information |

| 10/31/22   | Neal Gardella: Updated file link to Google drive                   |

| 11/16/22   | Connor Owen: Updated references to be in IEEE format.              |

Table 1.4: Revision Table 1

#### 2 Impacts and Risks

#### 2.1 Design Impact Statement

The modern world, technology has a great impact on everyone's lives and the security of each person is of utmost importance. Electronic devices give this security but have their own vulnerabilities and impacts on not only the environment but our social landscape as a whole. According to [3] the widespread implementation of electronic keys and locks has improved the safety and quality of life for students at an OK state college.

Smart locks are rising in popularity as smart devices become more commonly used and accessible to the average person, causing smart locks to become more ingrained in modern culture. This culture has been termed "ubiquitous culture" [4]. Since this ubiquitous culture is becoming more prevalent due to the use of smart locks, the vulnerabilities of those devices become vulnerabilities in the network, creating an impact on modern culture and by extension, society as a whole.

Technology is moving at a rapid pace and the security measures in smart locks are lagging behind. This allows attackers to gain access to a consumer's home and all smart home devices through inherent vulnerabilities in the hardware. As demonstrated in [5], there are security vulnerabilities in the cutting-edge smart locks by Master Lock, the worst of which allows an attacker to gain management control of the lock. This may be addressed by starting a dialogue with the company to patch the more severe vulnerabilities so that the end consumer will feel safer in a culture driven by technology.

The economic trends show that more and more individuals, be they private users or large companies, are going towards electronic security in order to keep themselves and their own equity safe. Additionally, it has been projected through the 2022-2029 years that there will be a higher demand for more secure electronic security devices [6] This leaves those with funds able to keep themselves secure and those without prime targets for thieves and robbers. This can be addressed by providing extra security measures at a reasonable cost or in the prevention of thieving through extra policing methods. Another way this could be worked around is a make sure that the devices could be loaned to people if/when they need them at very discounted prices

The impact that our project will have on the environment comes down to the e-waste we are creating from our design. Not all e-waste can be recycled leading to disposal into landfills where toxins from the heavy metals can be absorbed into the soil, harming the surrounding environment and its ecosystem [7]. The use of leaded solder in our project as well will have an impact on the environment, so we will have a standard in place to ensure no area is left contaminated. Also, creating a design that only uses electronic parts that we can acquire on OSU's campus without the need to have a shipment of electronic parts delivered so that we never created a notable amount of carbon emissions

The potential to research and develop an attack that works reliably on every lock of the same model would have an extremely detrimental impact on the company that sells the lock as well as overall eroding consumer faith in electronic locks. One potential solution to this could be to implement some element of randomness or obfuscation within the lock's electronic timings. Introducing randomness would prevent a one size fits all hack to all locks of the same model.

## 2.2 Risks

| Description                      | Category                                                                   | Probability                                                                                                                                                                                                                                                                                                                            | Risk Impact                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Performance Indicator                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Action Plan                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|----------------------------------|----------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                  |                                                                            |                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Alert project partner, prevent future                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Logic Analyzer Overvolts         | Technical                                                                  | Low                                                                                                                                                                                                                                                                                                                                    | High                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Logic Analyzer stops working                                                                                                                                                                                                                                                                                                                                                                                                                                             | overvolting, and seek replacement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                  |                                                                            |                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | hardware                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Working with load colder         | Cofoty                                                                     | High                                                                                                                                                                                                                                                                                                                                   | High                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Solder is marked as loaded                                                                                                                                                                                                                                                                                                                                                                                                                                               | Wash hands after soldering and do                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Working with lead solder         | Salety                                                                     | High                                                                                                                                                                                                                                                                                                                                   | High                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Solder is marked as leaded                                                                                                                                                                                                                                                                                                                                                                                                                                               | not eat or drink near station                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Leaking aurophysic out of look   | Technical                                                                  | Madium                                                                                                                                                                                                                                                                                                                                 | Madium                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Look decen't reenend to get nin                                                                                                                                                                                                                                                                                                                                                                                                                                          | Try reset code to open the lock, and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Locking ourselves out of lock    | recrinical                                                                 | weatum                                                                                                                                                                                                                                                                                                                                 | weaturn                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Lock doesn't respond to set pin                                                                                                                                                                                                                                                                                                                                                                                                                                          | guess code based on previous inputs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                  |                                                                            |                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Set a requirement to upload notes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Note upkeep not met              | Organizational                                                             | Low                                                                                                                                                                                                                                                                                                                                    | Medium                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Notes are not uploaded to Drive                                                                                                                                                                                                                                                                                                                                                                                                                                          | every meeting and reach out to member                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                  |                                                                            |                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | for their notes.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                  |                                                                            |                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | To discuss the legal liability of                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Release of vulnerabilities       | Safety/Public Health                                                       | Low                                                                                                                                                                                                                                                                                                                                    | High                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Project partner is informed of vulnerabilities                                                                                                                                                                                                                                                                                                                                                                                                                           | vulnerability with project partner                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                  |                                                                            |                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | and proceed with student wellbeing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                  |                                                                            |                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | in mind                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| AMC Lab Classed                  | Organizational                                                             | Law                                                                                                                                                                                                                                                                                                                                    | Llink                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Keyeerd eesee denied                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Move to Dearborn lab and use                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| AIVIS Lab Closed                 | Organizational                                                             | LOW                                                                                                                                                                                                                                                                                                                                    | High                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Reycard access denied                                                                                                                                                                                                                                                                                                                                                                                                                                                    | oscilloscope for analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Desired components not available | Technical                                                                  | Modium                                                                                                                                                                                                                                                                                                                                 | Modium                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Lipship to progress with timing analysis                                                                                                                                                                                                                                                                                                                                                                                                                                 | Select alternative component                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Desired components not available | recrimical                                                                 | wearam                                                                                                                                                                                                                                                                                                                                 | wearan                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | onable to progress with timing analysis                                                                                                                                                                                                                                                                                                                                                                                                                                  | that can achieve similar outcome                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| ESD Domogo                       | Technical                                                                  | Low                                                                                                                                                                                                                                                                                                                                    | High                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Electropic parts (microcontroller) atop working                                                                                                                                                                                                                                                                                                                                                                                                                          | When using breadboard and prototyping we will use                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| ESD Damaye                       | recrimical                                                                 | LOW                                                                                                                                                                                                                                                                                                                                    | riigii                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Electronic parts (microcontroller) stop working                                                                                                                                                                                                                                                                                                                                                                                                                          | ESD hand straps to help protect against damage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                  | Working with lead solder Locking ourselves out of lock Note upkeep not met | Logic Analyzer Overvolts     Technical       Working with lead solder     Safety       Locking ourselves out of lock     Technical       Note upkeep not met     Organizational       Release of vulnerabilities     Safety/Public Health       AMS Lab Closed     Organizational       Desired components not available     Technical | Logic Analyzer Overvolts         Technical         Low           Working with lead solder         Safety         High           Locking ourselves out of lock         Technical         Medium           Note upkeep not met         Organizational         Low           Release of vulnerabilities         Safety/Public Health         Low           AMS Lab Closed         Organizational         Low           Desired components not available         Technical         Medium | Logic Analyzer Overvolts     Technical     Low     High       Working with lead solder     Safety     High     High       Locking ourselves out of lock     Technical     Medium     Medium       Note upkeep not met     Organizational     Low     High       Release of vulnerabilities     Safety/Public Health     Low     High       AMS Lab Closed     Organizational     Low     High       Desired components not available     Technical     Medium     Medium | Logic Analyzer Overvolts       Technical       Low       High       Logic Analyzer stops working         Working with lead solder       Safety       High       High       Solder is marked as leaded         Locking ourselves out of lock       Technical       Medium       Medium       Lock doesn't respond to set pin         Note upkeep not met       Organizational       Low       Medium       Notes are not uploaded to Drive         Release of vulnerabilities       Safety/Public Health       Low       High       Project partner is informed of vulnerabilities         AMS Lab Closed       Organizational       Low       High       Keycard access denied         Desired components not available       Technical       Medium       Medium       Unable to progress with timing analysis |

## 2.3 References and File Links

#### 2.3.1 References