# Plasma Speaker

ECE 441-443 - Senior Design

2021 - 2022

Kyle Barton, Ian Scott Paul, Jeffery Unrein, Zhenglun Yang

# 1. Overview

# 1.1 Executive summary

The plasma speaker project aims to develop a functional speaker by creating and controlling plasma produced by an electric arc. This technology has been demonstrated to be capable of producing speakers with excellent replication of high-frequency sound.[1][2] Plasma speakers are used in place of a solid diaphragm speaker for the tweeters in some very high-end audio systems due to the material limitations of the solid diaphragm.[1] Our system functions by creating plasma between two electrodes and modulating alternating electrical current passing through the plasma so that the ionized air responds to the produced magnetic field. The resulting movement of ionized particles interacting with the surrounding air creates sound waves. Our goal is to produce an appealing, safe, and easy-to-use plasma speaker design for display in Kelley Engineering Center.

# 1.2 Team Communication Protocols and Standards

| Name           | Phone Number   | Email                    | Role                                      |

|----------------|----------------|--------------------------|-------------------------------------------|

| Kyle Barton    | (360) 953-0253 | bartokyl@oregonstate.edu | Digital Design                            |

| Jeffrey Unrein | (503) 910-0398 | unreinj@oregonstate.edu  | Power System/ Plasma<br>Generation Design |

| Zhenglun Yang  | (541) 740-0929 | yangz5@oregonstate.edu   | Software Design                           |

| Ian Scott Paul | (541) 730-2000 | paulia@oregonstate.edu   | Analog Design, FPGA<br>Design             |

### 1.2.1 Contact Information

## 1.2.2 Partner Communication Analysis

This project is run as a general partnership of the members. To generate an ideal end-user, we collaborated to establish goals and requirements based on our preferences and understandings of the system. As such our team has no external party to communicate with, we instead have dedicated bi-weekly meeting times to discuss the project's scope and direction.

### 1.2.3 Communication Protocols

- 1. Communication with Instructors:

- a. Questions will be asked during office hours and through email

- 2. Primary means of Communication:

- a. Group work and communications will be conducted through Discord.

- b. Text messages will be sent for in-person updates and team building.

- 3. Communication Style:

- a. Group members will ensure all ideas are heard, and that all members are on the same page before making decisions.

- 4. External Communication Etiquette:

- a. External communication about the project will be kept professional in manner.

- 5. Internal Communication Etiquette:

- a. Communication towards team members will remain polite at all times.

| Standard           | Protocol                                                                                                                                                                                                                                                                                                                                                                       |

|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Meetings           | <ul> <li>All group members will attend weekly meetings in Dearborn<br/>211 unless otherwise agreed upon by the entire team.</li> <li>All group members will be prepared for meetings and ready to<br/>participate.</li> <li>Meetings will be efficient and will follow a prepared meeting<br/>outline.</li> <li>Meetings will not go more than 20 minutes overtime.</li> </ul> |

| Documentation      | <ul> <li>Project documentation will be stored on the shared google drive.</li> <li>All documentation and artifacts will be of professional quality.</li> <li>Code will be commented on or self documenting.</li> <li>All diagrams will be readable and clear.</li> </ul>                                                                                                       |

| Individual Work    | <ul> <li>Progress on assigned tasks will be clearly communicated to the entire team.</li> <li>If it is uncertain if an assigned task will be completed within the original time frame, a solution will be chosen by the team.</li> </ul>                                                                                                                                       |

| Team Contributions | <ul> <li>Work will be split up only by the decision of the entire team<br/>and each member shall be tasked with a similar amount of<br/>work.</li> </ul>                                                                                                                                                                                                                       |

| Behavior           | <ul> <li>Team members should always have a positive inclusive attitude.</li> <li>Team members will include everyone's ideas and always provide a helping hand if needed.</li> </ul>                                                                                                                                                                                            |

#### 1.2.4 Team Standards

# 1.3 Gap Analysis

### 1.3.1 Need Gap

Our group is providing a rarely witnessed way to listen to music/sound. This provides a more diverse and inspirational listening experience for our end users. A plasma speaker also has no resonance or transient problems, thus an improvement over conventional solid diaphragm speakers. With a plasma arc having zero weight, this creates a faster response. This makes them ideal for ultra-high-quality reproduction of high frequencies. This speaker will also be displayed in Kelley Engineering to show the capabilities of Oregon State Electrical Engineering Students. The scope of this project is to create a prototype speaker design, thus all further assessments to take the speaker into production/market the speaker will be considered only once this project is completed.

### 1.3.2 Project Assumptions

Our project assumes that it will not be capable of completely replacing a traditional audio system, and will instead be focused only on producing high-frequency audio. Our research uncovered no plasma speaker systems capable of producing low-frequency audio without significant distortion due to physical limitations in the mechanism itself. Our project also assumes that it will provide a new and exciting way to listen to music.

### 1.3.3 Product Expectations & Fulfillment Description

Our project will be able to produce an accurate sound from user input. The user will provide a sound using a Bluetooth connection and the system will create that sound by using the ionized air to vibrate the surrounding air. It will also have a demo button so that it can be displayed in Kelley Engineering, and when pressed play "Hail to Old OSU." The speaker system will also have sufficient controls to change output volume and put the speaker in a standby mode. The entire system will be safe for the user and all those within the vicinity of the speaker. The entire system will be contained within a neat, user-friendly enclosure.

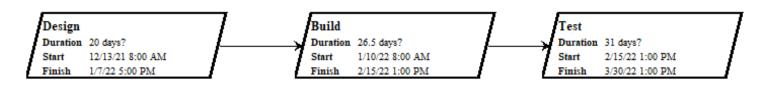

## 1.4 Proposed Timeline

The development of this system has been split into 3 phases: Design, Build and Test.

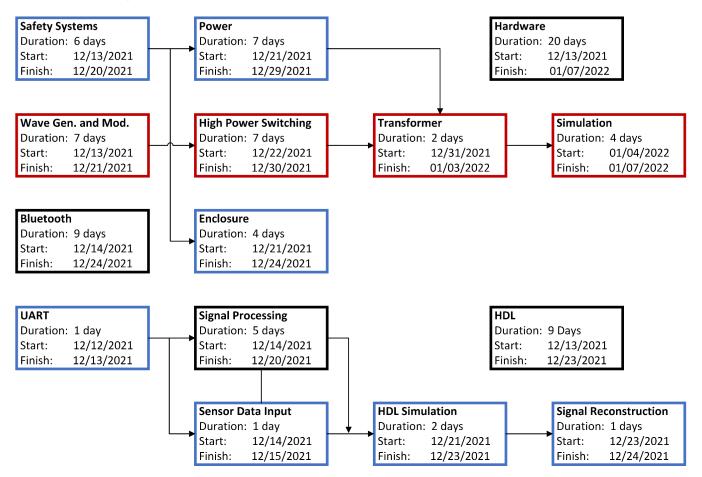

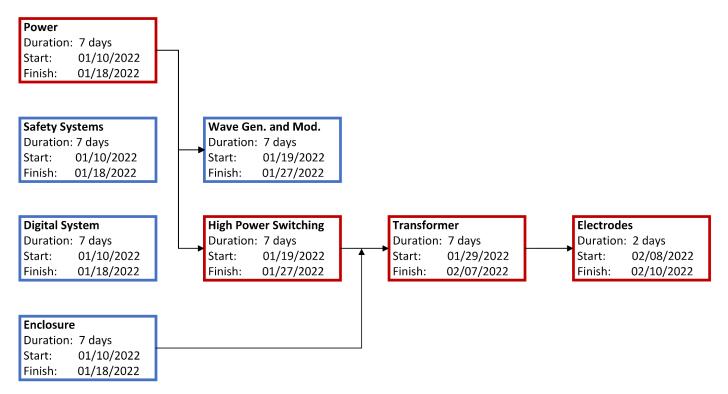

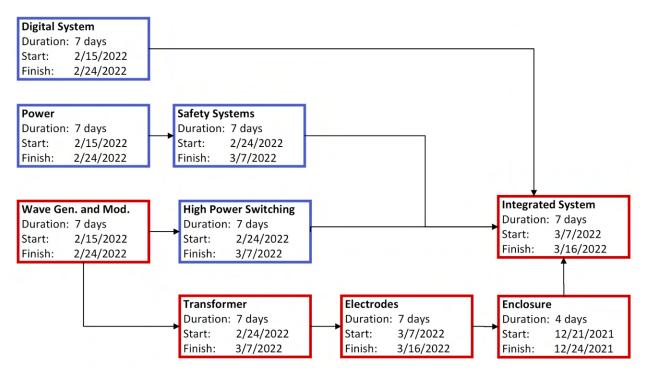

The phases of our project will be represented with a network generated from our Gantt chart in the following subsections. The full version of our Gantt chart with resource allocations is available in section 1.5.2. The critical path is highlighted in red.

#### 1.4.1 Design

The Design phase is split into two branches: HDL and Hardware. This phase is projected to last 20 days. Our targeted deliverables are schematics and block validation writeups.

#### 1.4.2 Build

The Build phase requires each group member to act on their design, and manufacture the physical system. This phase should result in the deliverable of several independent compatible modules ready for integration.

#### 1.4.3 Test

The Test phase ensures individual components function as expected, and can be integrated. Each module will be added and tested sequentially to help identify any errors in integration. The test phase should deliver a fully functional plasma speaker.

# 1.5 References and File Links

### 1.5.1 References (IEEE)

- [1] D. Severinsen and S. Gupta, "Design and Evaluation of Electronic Circuit for Plasma Speaker," *Proceedings of the World Congress on Engineering*, vol. II, 2013.

- [2] "Wireless/Wired Automatic Switched Plasma Tweeter & speaker ..." [Online]. Available: http://iosrjournals.org/iosr-jece/papers/Vol.%2012%20Issue%202/Version-2/D202022833 .pdf. [Accessed: 13-Nov-2021].

#### 1.5.2 File Links

Electrical Arc Speaker Team Drive - <u>link</u> Project Management Guidelines - <u>link1</u> - <u>link2</u> Gantt Chart - <u>link</u>

# 1.6 Revision Table

| Date       | Торіс                 | Revision                                                                                               |

|------------|-----------------------|--------------------------------------------------------------------------------------------------------|

| 12/03/2021 | Section 1.4           | Kyle, Ian: Revised timeline to be readable                                                             |

| 11/30/2021 | Section 1.5.2         | Jeffrey: Add a clickable link                                                                          |

| 11/30/2021 | Section 1.1           | lan: Updated executive summary to reflect new project goal to display in KEC                           |

| 11/30/2021 | Section 1.2.4         | Jeffrey: Formatted so text is in a table                                                               |

| 11/30/2021 | Section 1.2.2         | Ian and Kyle: Updated project partner<br>communication preferences and added<br>model user description |

| 11/12/2021 | Section 1.5           | Kyle: Updated citations to IEEE format                                                                 |

| 11/12/2021 | Section 1.3           | Kyle: Updated gap analysis to better describe the project expectations                                 |

| 11/11/2021 | Sections 1.2.2, 1.2.3 | Kyle: Further revision of communication protocols and team standards                                   |

| 11/08/2021 | Section 1.4.2         | Kyle: Revised project phases with more detail                                                          |

| 11/08/2021 | Sections 1.2.2, 1.2.3 | Kyle: Added new communication protocols and split up team standards                                    |

| 11/08/2021 | Section 1.4.1         | Ian: Added timeline                                                                                    |

| 10/29/2021 | Sections 1.1, 1.3.2   | Ian: Updated Executive Summary and assumptions                                                         |

| 12/02/2021 | Section 1.4           | lan and Kyle: Revised Timeline, Created Gantt chart and task network.                                  |

# 2. Requirements, Impacts, and Risks

# 2.1 Requirements

### 2.1.1

Project Partner Requirement: The system shall produce recognizable audio.

Engineering Requirement: Audio recognition technology "Shazam" will be able to correctly identify the source audio.

Verification method:

- 1. Power on the system and connect a bluetooth capable device that will play music.

- 2. Position another device with music recognition software "Shazam" near the enclosure.

- 3. Play music through the bluetooth speaker.

- 4. Process the audio with Shazam.

- 5. Verify the recognised song is the same as the source.

### 2.1.2

Project Partner Requirement: The system shall be responsive.

Engineering Requirement: The system begins playing audio through the arc within 2 seconds of the music being un-paused.

Verification method:

- 1. Power on system, connect to bluetooth, and start the flow of helium gas

- 2. Verify arc is not active

- 3. Un-pause music and verify arc is activated and playing audio within 2 second time frame

### 2.1.3

Project Partner Requirement: The system is safe to use.

Engineering Requirement: The system shall have an emergency shutoff switch that powers off the arc in less than 1 second.

Verification method:

- 1. Power system on and activate the arc by playing music

- 2. Using a slow motion phone video camera, place a stopwatch within frame and begin recording and begin the stopwatch

- 3. Also within frame and with both the stopwatch and the speaker arc on, flip the emergency shutoff switch

- 4. Stop recording after 3 seconds. Verify in the slow motion video that the arc was disabled within 1 second of the emergency shutoff switch being flipped

2.1.4

Project Partner Requirement: The system shall use helium gas to produce and arc. Engineering Requirement: The system shall produce its arc in the presence of helium gas. Verification method:

- 1. Power on the system and connect bluetooth.

- 2. Attempt to play music.

- 3. Verify that the system is unable to produce plasma.

- 4. Activate the flow of helium.

- 5. Verify the arc activates.

### 2.1.5

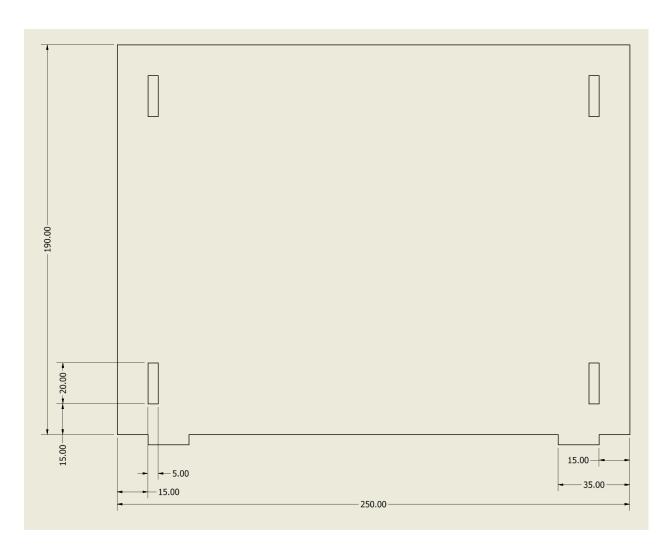

Project Partner Requirement: The system is contained in a safe enclosure Engineering Requirement: The system's enclosure shall not allow users to come within 2 inches of the arc.

Verification Method:

- 1. Place electrodes within enclosure as they will be for final system

- 2. Insert measuring device through enclosure from each of the 5 sides

- 3. Measure from each side the distance between the environment (outside the enclosure) to the end of each electrode probe

- 4. Ensure that all measurements give a minimum of 2 inches from electrode probe to environment

### 2.1.6

Project Partner Requirement: The system must be reliable.

The system will be able to play music for 60 seconds without overheating Verification Method:

- 1. Power on System and start helium flow.

- 2. Start input audio from connected bluetooth device

- 3. Use stopwatch to time system

- 4. Enjoy music for a minute.

2.1.7

Project Partner Requirement: The system's arc is only active when music is playing. Engineering Requirements: System's electrical arc shall shut off within 2 seconds of the input audio signal being paused, and remain off until the audio signal is resumed. Verification method:

- 1. Power system on and begin playing sound through Bluetooth audio, verify electrical arc is active

- 2. Pause audio

- 3. Verify that the electrical arc is no longer active within 2 seconds of pausing

### 2.1.8

Project Partner Requirement: The system is Bluetooth compatible.

Engineering Requirements: The system shall be able to play audio transmitted from a Bluetooth source

Verification method:

- 1. Power on the system and start helium flow.

- 2. Using a Bluetooth 4.0 compatible audio transmission device, investigate the Bluetooth connection menu.

- a. This will be different depending on the outside device used.

- b. The outside device must have its bluetooth mode active, and be set to "scan" or "search" for new devices.

- 3. Locate a device called "BT5.0 Audio"

- 4. Attempt to connect to the device via Bluetooth

- 5. Verify the connection is made and the system is recognized as an audio output.

- 6. Play some audio at full volume.

- 7. Verify arc speaker activates.

# 2.2 Design Impact Statement

This section presents a brief overview of the impacts of our design for readability. A detailed analysis of the impacts is available here: <u>Full Design Impact Assessment</u>.

### 2.2.1 Public Health: Avoiding Ozone & Preventing Burns

Due to the high risk of electric shock and burns associated with voltages high enough to break down air, the safety of the designers and end users of the system is a priority.

Following our risk assessments our team opted to use helium gas as it is easier to ionize, allowing for a lower voltage to create an electric arc. Since the typical composition of air is mostly Nitrogen and Oxygen gas ( $N_2$  and  $O_2$ ), its ionization ultimately allows for the formation of Nitrous Oxide ( $N_2O$ ), Nitric Oxide (NO), and Ozone( $O_3$ )[1]. The use of helium stops the formation of these gasses by forming the arc in an area saturated with the monatomic gas.

Due to the lightest noble gas only having two protons, it's relatively easy to ionize. The significantly lower voltage required reduces both the risk of electric shock and the risk of thermal burns from touching overheated components within the system.

### 2.2.2 Welfare Impacts

One potential welfare impact to consider is the dangers of loud noise. Although this is a smaller source of risk within the scope of our project, it is still important to examine. Our electrical arc speaker will be designed to operate at safe loudness levels, but malfunctions in the system could cause unpredicted loud noises. Electrical failures at high voltage often produce sudden 'popping' noises that are short term bursts which can be in the excess of 130+ decibels. Yale University School of Medicine research shows that a single burst of 140 dB can cause long term effects and lead to hearing loss [2].

### 2.2.3 Culture and Society: Animal Testing and Cultural Impacts

We did not end up performing animal testing, but the center frequency for our system is just above the range of humal hearing but within the range of many other animals[3]. Simply said, as of right now running our system is like blowing into a dog whistle.

Due to the high cost and appant safety considerations, it is unlikely that this will become a common consumer replacement of current speaker systems. That said, they can still be a useful educational and inspirational tool given the wide impact of music.

### 2.2.4 Environmental Considerations: No Light Matter.

One well documented environmental impact of electronics is the known problem of E-waste. Every electronic device has a limited lifespan and will need to be disposed of at some point. A study by Brett Robinson showed that the elements that make up the most harmful environmental contaminants are "Pb, Sb, Hg, Cd, Ni, polybrominated diphenyl ethers (PBDEs), and polychlorinated biphenyls (PCBs) [4]." Analyzing our system, it is likely that the end product will only contain one or two of these targeted high impact pollutants; polychlorinated biphenyls and possibly lead. To mitigate this risk and be thoughtful of the eventual disposal of the electrical arc speaker, one option is to consider RoHS compliant lead-free components and manufacturing. This manufacturing technique is popular for the European market due to stricter environmental regulations. The benefit of it being fairly widely used is that there is infrastructure set up already to create a design to be RoHS lead-free. Many chip manufacturers create and sell lead-free versions of their chips at only a marginally higher price. The biggest sacrifice to going lead-free is the manufacturing and assembling of your PCBs as it limits your package and solder styles. For example, large tight pitch BGAs are often difficult and expensive to implement lead-free as the reduced flow of the lead-free solder makes them harder to align and more prone to cracking.

Along with this, the choice to use Helium is double-sided. Helium is a noble gas, and is lighter than the majority of the atmosphere. This means that it won't bind to anything and instead will escape the planet by moving to the very outer edge of space. It is a particularly important element to conserve until its production in nuclear fission facilities is made into a reality. Currently the only helium accessible to us is a byproduct of natural gas extraction, where it is still produced by radioactive decay. [1]

### 2.2.5 Economic Factors

The major economic impacts of the electrical arc speaker will likely fall on the design team. The worldwide Covid-19 pandemic has had a major impact on all areas of the electronics market. A recent study from IEEE that investigates this impact and found that there is an increased need in the consumer electronics market, along with a decreased supply in the consumer electronics market [5]. Basic supply and demand tells us that these two factors cause severe price increases. If our speaker is cheap, easy to manufacture, and easy to source the materials for, we can make an impact on this squeezed market and help equalize the economic factors back to a normal level.

The other more direct impact that the Covid-19 pandemic will have on our project is the current state of the semiconductor and IC market. A study by the Federal Reserve Bank of Cleveland analyzes the behind the scenes of the current microchip shortage that likely everyone is now aware of. The study finds that the weak points in the supply chain for microchips collapsed when Covid hit, and thus a shortage arose [6]. The current lead time on specialized ICs is very commonly 52+ weeks or even listed as out of production.

Given it's primary public use as filling balloons, the only local sourcing possible was through a party supply store where we were charged \$50 per tank.

# 2.3 Risk Assessment

| Risk<br>ID | Risk description                                             | Categor<br>y      | Probably | Impact | Performanc<br>e indicator                                                                  | Responsi<br>ble party | Action<br>plan                                 |

|------------|--------------------------------------------------------------|-------------------|----------|--------|--------------------------------------------------------------------------------------------|-----------------------|------------------------------------------------|

| 1          | Member sick                                                  | Team              | М        | L      | Team<br>member not<br>able to join<br>team<br>meetings<br>due to a<br>sickness             | Jeffrey U.            | Retain                                         |

| 2          | Member injured                                               | Team              | L        | Н      | Team<br>member not<br>able to get<br>required<br>work done<br>due to<br>external<br>injury | Kyle<br>Barton        | Retain                                         |

| 3          | Chip shortage<br>delays                                      | Timeline<br>/Cost | М        | Μ      | Lead times<br>on Chips<br>are more<br>than 2<br>months                                     | lan Scott<br>Paul     | Reduce<br>by<br>ordering<br>early and<br>extra |

| 4          | Part of the<br>project did not<br>work (Power,<br>code, etc) | Team              | М        | Н      | A team<br>member<br>should help<br>each other<br>to figure out<br>the problem              | Yang                  | Retain                                         |

| 5          | Team<br>communication<br>issues                              | Team              | L        | Н      | Not<br>everyone<br>responding<br>or<br>participating<br>in group<br>chats/<br>meetings     | Kyle<br>Barton        | Reduce<br>by<br>mediation                      |

| 6          | PCB long lead times                                          | Team              | М        | М      | Lead times<br>on PCBs<br>are more<br>than 2<br>months                                      | Kyle<br>Barton        | Reduce<br>by<br>planning<br>ahead              |

# 2.4 References and File Links

### 2.4.1 References (IEEE)

- [1] Kroschwitz, Jacqueline I., executive editor, and Mary Howe-Grant, editor. Encyclopedia of Chemical Technology, 4th edition. John Wiley and Sons, Inc., 1993.

- [2] Rabinowitz, P.M. "Noise-Induced Hearing Loss," Yale University School of Medicine, New Haven, Connecticut. American Family Physician, no. 61, p. 2749-2756, Oct 2000.

- [3] Purves D, Augustine GJ, Fitzpatrick D, et al., editors. Neuroscience. 2nd edition.

Sunderland (MA): Sinauer Associates; 2001. The Audible Spectrum. Accessed on: Dec.

2, 2021. Available: <u>https://www.ncbi.nlm.nih.gov/books/NBK10924/</u>

- [4] B. H. Robinson, "E-waste: An assessment of global production and environmental impacts," Science of The Total Environment, vol. 408, no. 2, pp. 183–191, 2009.

- [5] T. Coughlin, "Impact of covid-19 on the Consumer Electronics Market," IEEE Consumer Electronics Magazine, vol. 10, no. 1, pp. 58–59, 2021.

- [6] J. E. Dunn, "Covid-19 and Supply Chains: A year of evolving disruption," Cleveland Fed District Data Briefs, 2021.

### 2.4.2 File Links

Complete risk register with progress updates - link

Complete engineering requirements with progress updates - link

# 2.5 Revision Table

| Date       | Торіс             | Revision                                                   |

|------------|-------------------|------------------------------------------------------------|

| 05/06/2022 | Section 2.2       | Ian and Kyle: Added DIA and updated citations              |

| 03/06/2022 | Requirement 2.1.5 | Kyle: Updated requirement 2.1.5 verification method        |

| 11/30/2021 | Section 2.1       | Team: Fully reworked requirements and verification methods |

| 11/30/2021 | Section 2.4                                                        | Jeffrey: Separated into two different subsections                          |

|------------|--------------------------------------------------------------------|----------------------------------------------------------------------------|

| 11/11/2021 | Not enough requirements<br>Some Requirements are not<br>measurable | Team: Reworded some of the requirements.<br>Added additional requirements. |

| 11/11/2021 | Performance Indicator not filled out                               | Jeffrey: Filled out performance indicator for all risk                     |

| 11/30/2021 | Section 2.3                                                        | Yang: Update new risks                                                     |

# 3. Top-Level Architecture

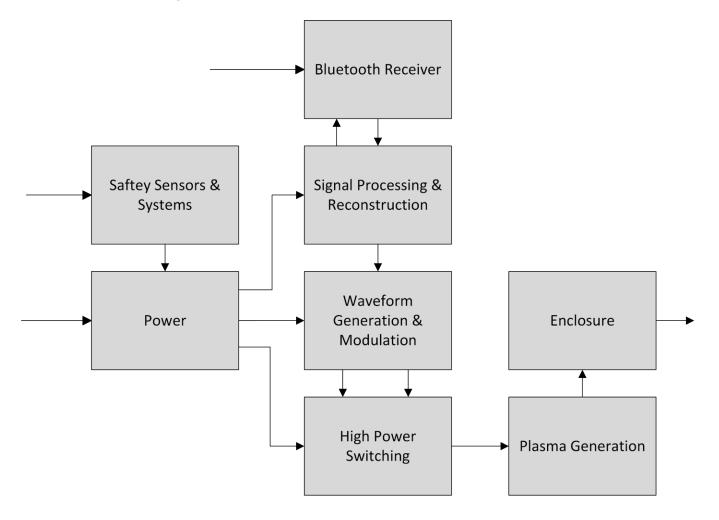

# 3.1 Block Diagram

# 3.2 Block Descriptions

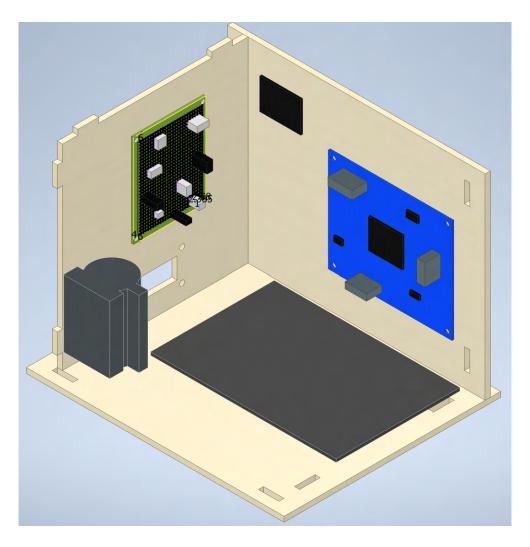

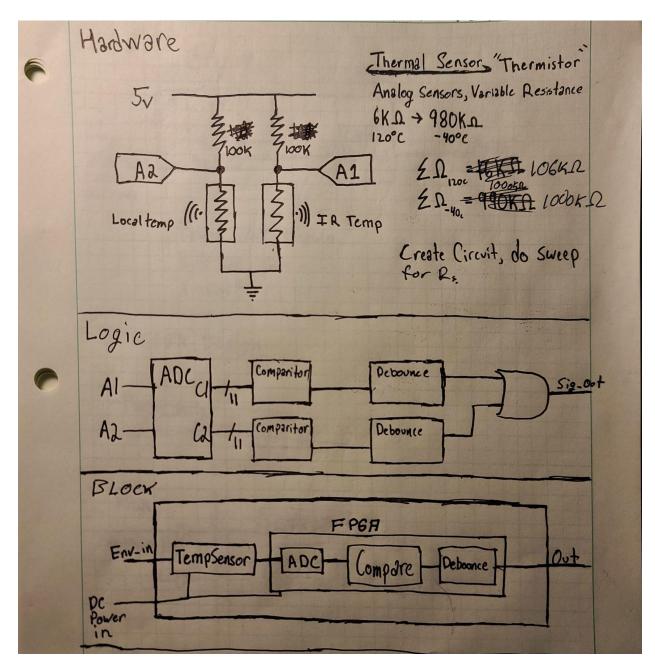

### 3.2.1 Safety, Sensors, & Systems

Block Champion: Ian Scott Paul

This block is to ensure our system is safe to use for ourselves and users other than ourselves. Our team's safety system will have an emergency cutoff switch for an outside user to press at any time of the system's operation. This block will be directly connected to the power block so that the main power can be shut off at any point. This block will also be responsible for monitoring the system's sensors and delivering digital control to all necessary components. This block will also be responsible for triggering fault signals based on sensor data. Another function of the Safety system is to put the speaker into an 'idle mode' when no audio input is detected by the Bluetooth receiver block. All of this functionality will be implemented on the system's FPGA.

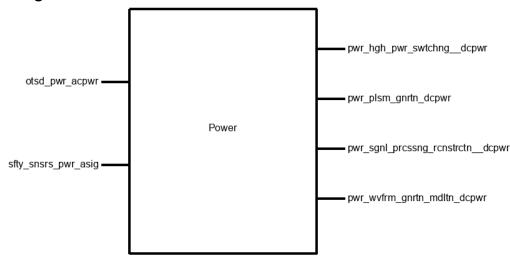

### 3.2.2 Power

#### Block Champion: Jeffery Unrein

This block will be used to power the entire Electric Arc system. This block will take in 120 VAC from a wall plug-in and output two different DC voltages. One of these voltages will power the FPGA board that powers the BlueTooth, PWM, and safety sensor blocks. The other voltage will power the high power switching and plasma generation blocks. These two separate voltages will ensure that each component in those blocks is receiving the right amount of power.

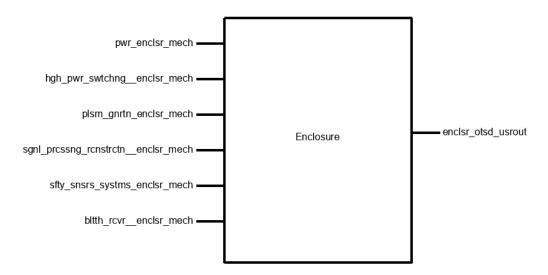

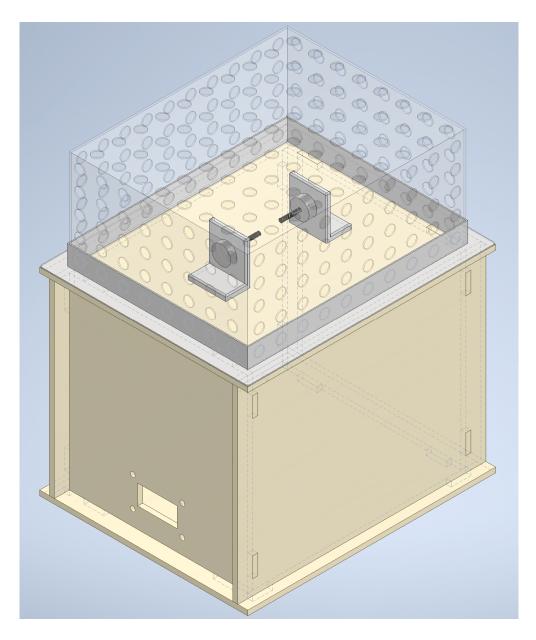

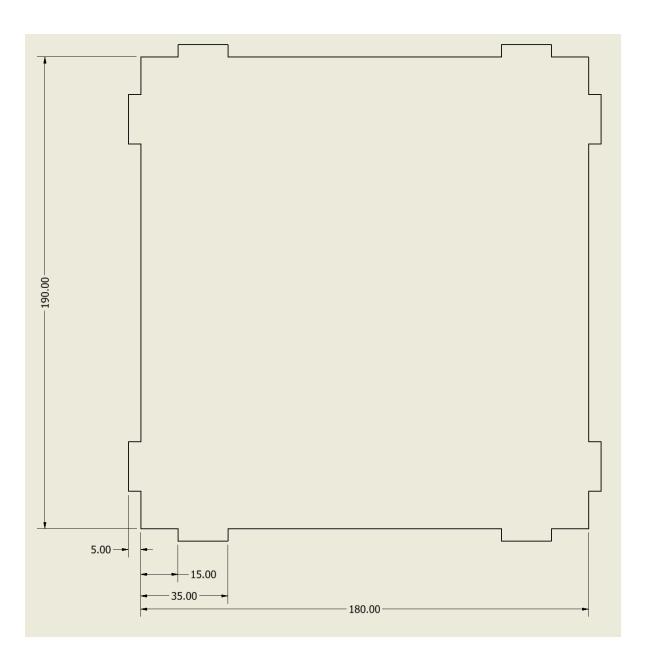

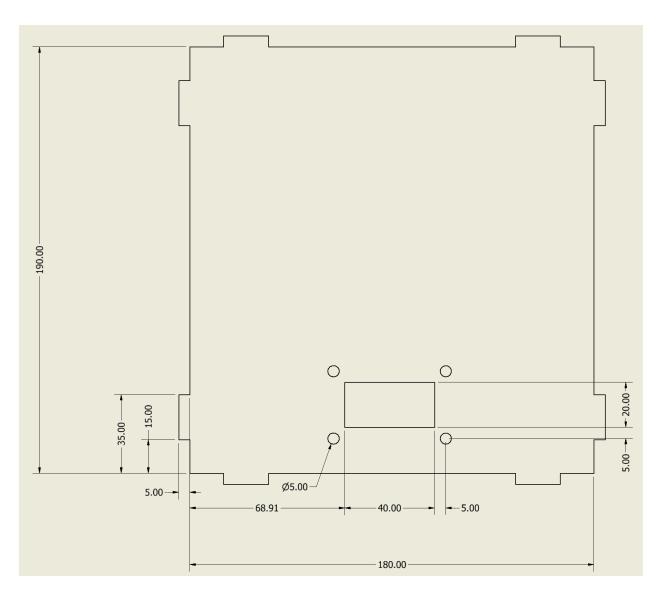

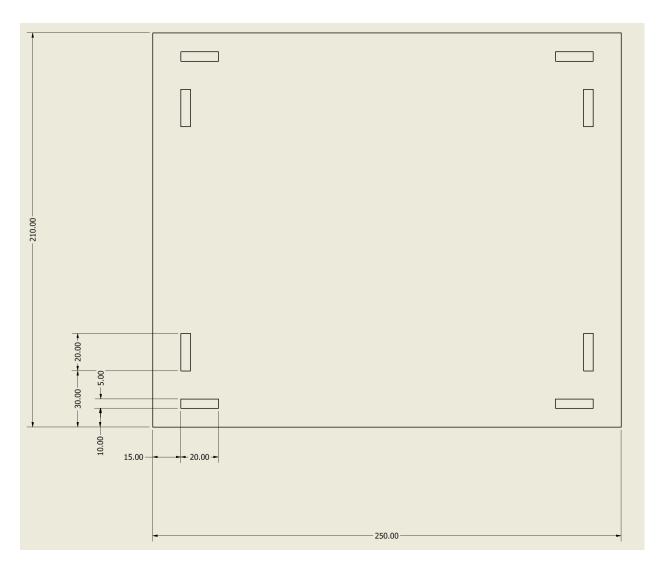

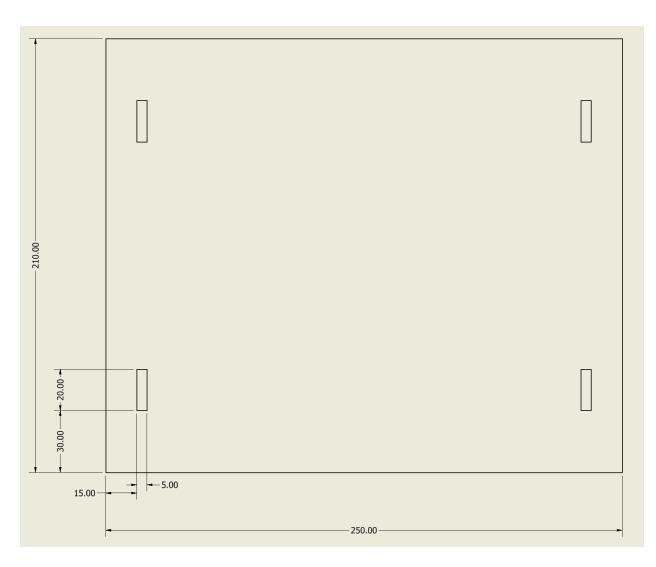

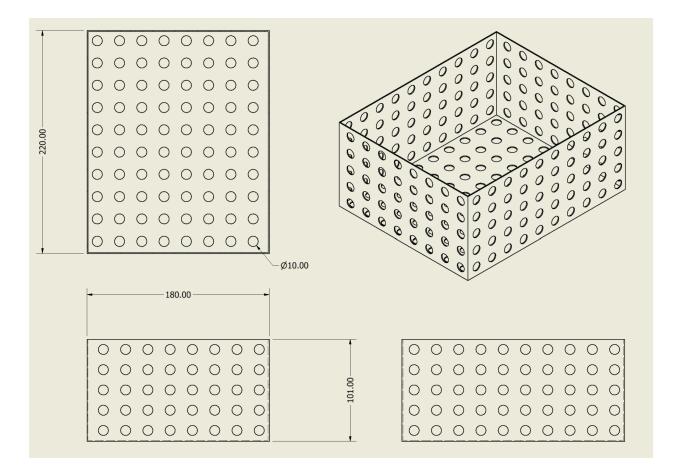

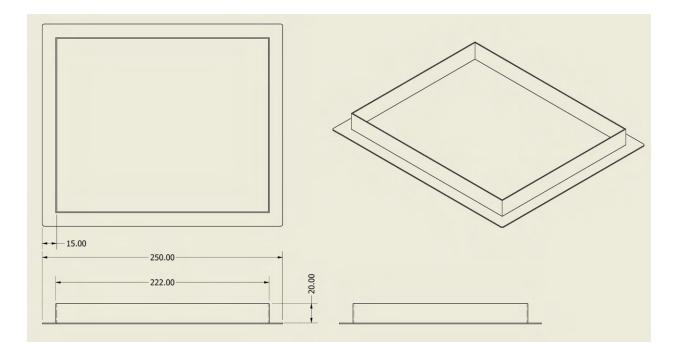

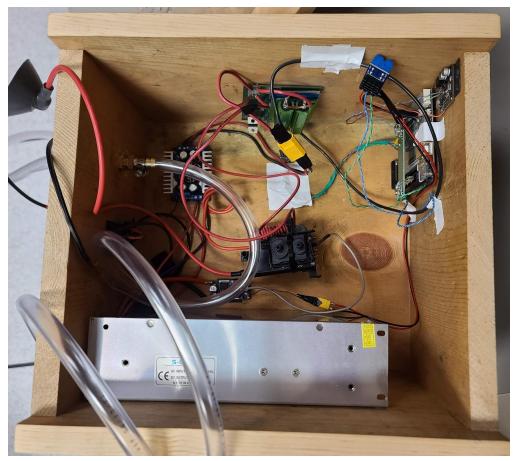

### 3.2.3 Enclosure

#### Block Champion: Kyle Barton

This block is the physical enclosure for the entire electrical arc speaker system. This includes the mounting and layout of all the various subsystems in a well-thought-out and efficient manner. This block will also facilitate the speaker system's ability to connect to the end-user. This enclosure will be aesthetically pleasing and mimic a professional/commercial level design. This enclosure will also be designed so that the system is safe to the end-user, preventing any contact or proximity to the high voltage signals. Other aspects of this block include good acoustic properties and an intuitive and easily accessible button to play the speaker's demo song.

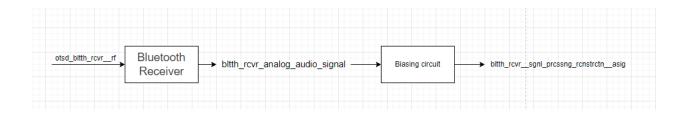

#### 3.2.4 Bluetooth Receiver

#### Block Champion: Zhenglun Yang

The Bluetooth Receiver block will wirelessly receive user input and digital music data from outside the system and deliver them to the Signal Processing and Reconstruction block. This enables the system to receive the music data digitally, so no sampling has to be done before signal processing can occur. The Bluetooth receiver also adds a layer of safety by enabling the user to interact with the system remotely. The system will show up to other Bluetooth devices as "Plasma Speaker", and will be flagged for them as an audio output device.

### 3.2.5 Signal Processing and Reconstruction

Block Champion: Ian Scott Paul

As plasma speakers typically have significant distortion due to the movement of the arc and displacement of the air, it is necessary to perform signal processing on the input audio to counter the effects caused by the rest of the system. By creating a parameterizable finite impulse response filter in Matlab and implementing it on an FPGA, real-time signal processing of the streamed digital audio data is achieved. Much of the fine-tuning will require the entire system to be implemented in order to calculate the actual frequency response.

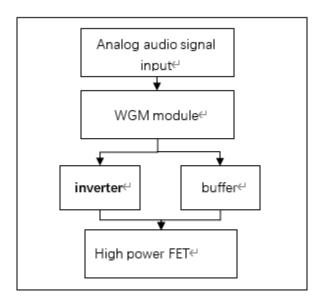

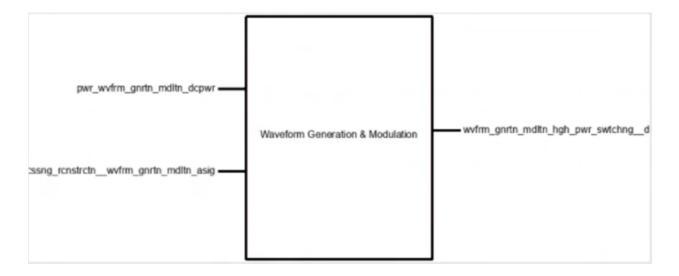

### 3.2.6 Waveform Generation and Modulation

Block Champion: Zhenglun Yang

Taking the analog audio signal as an input, the WGM block will modify the duty cycle of a square wave. This modulation is what implants the audio within the eventual high power signal. The modulated square wave is then split into a buffer and an inverter to create mirrored signals perfectly in phase. This is used to create the push-pull characteristics needed to sustain high voltage. This will be implemented with 3 different integrated circuits, one for pulse width modulation, one buffer, and one inverter.

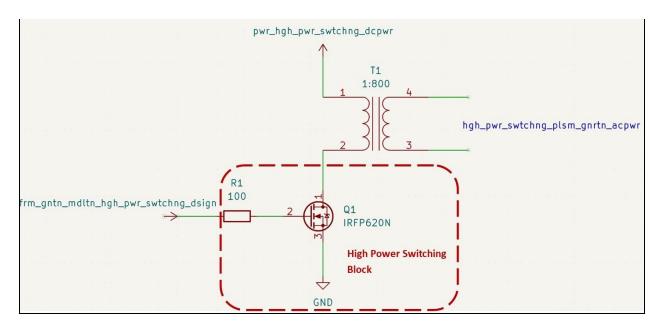

### 3.2.7 High Power Switching

Block Champion: Kyle Barton

Since the integrated circuits in the Waveform Generation and Modulation block are not capable of providing enough power to the Plasma Generation block, the waveforms are instead used to drive high power FETs. These will be large transistors with heatsinks.

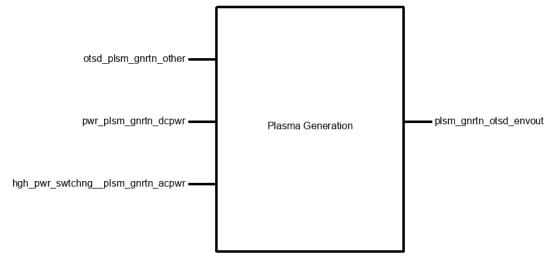

### 3.2.8 Plasma Generation

Block Champion: Jeffrey Unrein

The Plasma Generation block consists of the transformer and electrodes used to amplify the voltage to create the electric arc. This is used to step up the voltage nearly 800 times for the electrodes. This block may also include large capacitors to speed up the circuit's transient response and provide instant voltage to the electrodes for the high-frequency sound signals.

# 3.3 Interface Definitions

| Name                     | Properties                                                                                                                                                                                 |

|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| otsd_pwr_acpwr           | <ul> <li>Inominal: 15 Amps</li> <li>Other: 60 Hz</li> <li>Vnominal: 120 Volts</li> </ul>                                                                                                   |

| otsd_sfty_snsrs_envin    | <ul> <li>Temperature (Absolute): 100<br/>Celsius (IR temp)</li> <li>Temperature (Absolute): 100<br/>Celsius (Air/sensor temp)</li> <li>Water: No water. 0CFS, no<br/>immersion.</li> </ul> |

| otsd_bltth_rcvrrf        | <ul> <li>Other: Vmin: 0V Vmax: 5V Imin:<br/>0 mA Imax: 10 mA</li> <li>Protocol: WAV/MP3</li> <li>Protocol: Bluetooth 4.0 A2DP</li> </ul>                                                   |

| pwr_hgh_pwr_swtchngdcpwr | <ul> <li>Inominal: 1A</li> <li>Ipeak: 5A</li> <li>Vmax: 40V</li> <li>Vmin: 24V</li> </ul>                                                                                                  |

| pwr_plsm_gnrtn_dcpwr     | <ul> <li>Inominal: 3 Amps</li> <li>Ipeak: 4.5 Amps</li> <li>Vmax: 20 Volts</li> <li>Vmin: 10.5 Volts</li> </ul>                                                                            |

| pwr_sgnl_prcssng_rcnstrctn_dcpwr             | <ul> <li>Inominal: 150milliAmps</li> <li>Ipeak: 500 milliAmps</li> <li>Vmax: 5.5 Volts</li> <li>Vnominal: 5 Volts</li> </ul> |

|----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|

| pwr_wvfrm_gnrtn_mdltn_dcpwr                  | <ul> <li>Inominal: 0.004 Amp</li> <li>Ipeak: 0.100 Amps</li> <li>Vmax: 11 Volts</li> <li>Vmin: 5 Volts</li> </ul>            |

| hgh_pwr_swtchngplsm_gnrtn_acpwr              | <ul> <li>Inominal: 1A</li> <li>Vmax: 40 VAC</li> <li>Vmin: 24 VAC</li> </ul>                                                 |

| sgnl_prcssng_rcnstrctnwvfrm_gnrtn_mdltn_asig | <ul> <li>Max Frequency: 20K Hz</li> <li>Vmax: 1.5V</li> <li>Vrange: +-1V</li> </ul>                                          |

| sgnl_prcssng_rcnstrctnbltth_rcvrdcpwr        | <ul> <li>Inominal: 5m A</li> <li>Vmax: 5 V</li> </ul>                                                                        |

| sfty_snsrs_pwr_asig                          | <ul> <li>Other: Active High</li> <li>Vmax: 3.5 Volts</li> <li>Vrange: 0 - 3.5 Volts</li> </ul>                               |

| wvfrm_gnrtn_mdltn_hgh_pwr_swtchngasig        | <ul> <li>Max Frequency: 25K Hz</li> <li>Other: Logic Level: 10V</li> </ul>                                                   |

| bltth_rcvr_sgnl_prcssng_rcnstrctn_dcpwr      | <ul> <li>Other: Vrange: +-1V</li> <li>Other: Max Frequency: 20K Hz</li> <li>Vmax: 1.5V</li> </ul>                            |

# 3.4 Reference and File links

3.4.1 References (IEEE)

## 3.4.2 File Links

Student Portal - link

# 3.5 Revision Table

| Date       | Торіс                 | Revision                                                                     |

|------------|-----------------------|------------------------------------------------------------------------------|

| 5/1/2022   | Interface Definitions | Team: Complete Interface definitions in the student portal and insert table. |

| 12/1/2021  | Interface Definitions | Team: Complete Interface definitions in the student portal and insert table. |

| 11/30/2021 | Block Diagram         | Kyle: Reformatted block diagram with larger text and easier to read colors   |

| 11/22/2021 | Block Descriptions    | Team: Wrote block descriptions of our blocks                                 |

| 11/22/2021 | Block Diagram         | Team: Updated block diagram to an 8 block format from the original 12 blocks |

# 4. Block Validations

# 4.1 Power Block

### 4.1.1 Description

This block will be used to power the entire Electric Arc system. This block will take in 120 VAC from a wall plug-in and output two different DC voltages. One of these voltages will power the FPGA board that powers the bluetooth, PWM, and safety sensor blocks. The other voltage will power the high power switching and plasma generation blocks. These two separate voltages will ensure that each component in those blocks are receiving the right amount of power.

### 4.1.2 Design

### Black Box Diagram:

## Schematic:

| AC_DC_     | Converter           | Boost_Converter |                       |

|------------|---------------------|-----------------|-----------------------|

| AC_Powerin | DC+<br><br>DC-<br>4 | 1 Vin Vout 3    | {pwr_hgh_pwr_swtchng] |

|            |                     | Buck_Converter  |                       |

|            |                     | Vin Vout 3      | (pwr_fpga)            |

|            |                     |                 |                       |

### 4.1.3 General Validation

This block will utilize an AC - DC converter to convert AC power from a wall plug in and provide a steady DC output. It will then use 2 voltage regulators in parallel to supply two separate voltages to our system. By using voltage regulators instead of dropping down the voltage with resistors I will be able to ensure the correct amount of voltage is going to each of our components.

### 4.1.4 Interface Validation

| Interface Property | Why is this interface this value? | Why do you know that your<br>design details <u>for this block</u><br>above meet or exceed each<br>property? |

|--------------------|-----------------------------------|-------------------------------------------------------------------------------------------------------------|

|                    |                                   |                                                                                                             |

#### otsd\_pwr\_acpwr : Input

| Inominal: 15 Amps   | Current is based on how much<br>the breaker can handle. This is<br>the average amount of current<br>we plan on drawing. | The AC to DC converter max input current is rated to 15 Amps [1] |

|---------------------|-------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|

| Other: 60 Hz        | This is the frequency AC power switches at in the U.S                                                                   | The AC to DC converter max input frequency is rated to 63 Hz [1] |

| Vnominal: 120 Volts | This is the average voltage in a wall socket in the U.S                                                                 | The AC to DC converter voltage minimum is 110 Volts and its      |

|  | maximum is 220 Volts | [1] |

|--|----------------------|-----|

|--|----------------------|-----|

#### pwr\_plsm\_gnrtn\_dcpwr : Output

| Inominal: 3 Amps | This is the average amount of<br>current being drawn when arc<br>was established | Voltage regulators tend to need<br>the same input current as they do<br>output. The AC-DC converter is<br>able to produce a current of 40<br>Amps [1]                       |

|------------------|----------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| lpeak: 4.5 Amps  | This is the peak current that was drawn when creating the arc                    | Voltage regulators tend to need<br>the same input current as they do<br>output. The AC-DC converter is<br>able to produce a current of 40<br>Amps [1]                       |

| Vmax: 20 Volts   | This is the maximum voltage needed to produce the arc                            | I will use the Shenghao SH-PWS3<br>voltage regulator which has a<br>varying output voltage to satisfy<br>both the max and minimum<br>voltages needed to produce the<br>arc. |

| Vmin: 10.5 Volts | This is the minimum voltage needed to produce the arc                            | I will use the Shenghao SH-PWS3<br>voltage regulator which has a<br>varying output voltage to satisfy<br>both the max and minimum<br>voltages needed to produce the<br>arc. |

## pwr\_sgnl\_prcssng\_rcnstrctn\_dcpwr : Output

| Inominal:<br>150milliAmps | This is the nominal current used<br>by the components in this block<br>as tested by one of my<br>groupmates | Voltage regulators tend to need<br>the same input current as they do<br>output. The AC-DC converter is<br>able to produce a current of 40<br>Amps [1] |

|---------------------------|-------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| Ipeak: 500 milliAmps      | This is the peak current used by<br>the components in this block as<br>tested by one of my groupmates       | Voltage regulators tend to need<br>the same input current as they do<br>output. The AC-DC converter is<br>able to produce a current of 40<br>Amps [1] |

| Vmax: 5 Volts             | This is the maximum voltage                                                                                 | I will use a LM2596 voltage                                                                                                                           |

|                 | needed to ensure components<br>are provided enough power to<br>work. This was tested by one of<br>my groupmates                                | regulator that has a varying output<br>voltage to satisfy both the max and<br>minimum voltages needed by this<br>component                                |

|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| Vmin: 4.5 Volts | This is the minimum voltage<br>needed to ensure components<br>are provided enough power to<br>work. This was tested by one of<br>my groupmates | I will use a LM2596 voltage<br>regulator that has a varying output<br>voltage to satisfy both the max and<br>minimum voltages needed by this<br>component |

### $pwr\_wvfrm\_gnrtn\_mdltn\_dcpwr:Output$

| Inominal: 0.004 Amp | This is the nominal current used<br>by the components in this block<br>as tested by one of my<br>groupmates                                         | Voltage regulators tend to need<br>the same input current as they do<br>output. The AC-DC converter is<br>able to produce a current of 40<br>Amps [1]     |

|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| lpeak: 0.1 Amps     | This is the peak current used by<br>the components in this block as<br>tested by one of my groupmates                                               | Voltage regulators tend to need<br>the same input current as they do<br>output. The AC-DC converter is<br>able to produce a current of 40<br>Amps [1]     |

| Vmax: 11 Volts      | This is the maximum voltage<br>needed to ensure components<br>are provided with enough power<br>to work. This was tested by one<br>of my groupmates | I will use a LM2596 voltage<br>regulator that has a varying output<br>voltage to satisfy both the max and<br>minimum voltages needed by this<br>component |

| Vmin: 5 Volts       | This is the minimum voltage<br>needed to ensure components<br>are provided with enough power<br>to work. This was tested by one<br>of my groupmates | I will use a LM2596 voltage<br>regulator that has a varying output<br>voltage to satisfy both the max and<br>minimum voltages needed by this<br>component |

### sfty\_snsrs\_systms\_pwr\_asig : Input

| Vmax: 3.5 Volts | This is the maximum voltage that could be sent to switch. | I will be using the<br>SRD-12VDC-SL-C relay module<br>that can receive this max voltage<br>and turn off and on depending on<br>what signal is given. |

|-----------------|-----------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

|-----------------|-----------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| Vrange: 0 - 3.5 Volts | This is the range of possible<br>voltages that could be sent to<br>the switch | I will be using the<br>SRD-12VDC-SL-C relay module<br>that can receive these range of<br>voltages so that it knows when to<br>turn on and off. |

|-----------------------|-------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| Other: Active High    | When provided an active high of 3.5 volts. The switch will activate.          | I will be using the<br>SRD-12VDC-SL-C relay module<br>that once sent a active voltage<br>switches to shut off power                            |

#### 4.1.5 Verification Process

- 1. Plug in block to wall outlet.

- 2. Send a turn on signal to the switch to send power to each voltage regulator

- 3. Test pwr\_plsm\_gnrtn output maximum and minimum volatages.

- 4. Test pwr\_plsm\_gnrtn output nominal and peak currents

- 5. Test pwr\_sgnl\_prcssng\_rcnstrctn output maximum and minimum volatages.

- 6. Test pwr\_sgnl\_prcssng\_rcnstrctn output nominal and peak currents

- 7. Test pwr\_wvfrm\_gnrtn\_mdltn output maximum and minimum volatages.

- 8. Test pwr\_wvfrm\_gnrtn\_mdltn output nominal and peak currents

- 9. Send a off signal to the switch to shut off all power to system

- 10. Complete steps 3-8 to ensure no voltage or current is being outputed.

### 4.1.6 References and File Links

[1] Mulview, "500W single output switching power supply" S-500 series datasheet, Available: <u>http://m.microjpm.com/\_files/200006707-79dfe7ad65/S-500%20Series%20Datasheet.pdf</u> [Accessed: 18-Fed-2022].

#### 4.1.7 Revisions Table

| Торіс                         | Revision                                                         |

|-------------------------------|------------------------------------------------------------------|

| Descriptions changed - 5/6/22 | Updated descriptions and schematics to match most recent system. |

| Interface Properties - 3/4/22 | Updated interface properties to make block diagram update        |

| References changed 2/18/2022  | Changed the reference to actual component being used             |

| Additional information added 2/18/2022 | Added specific components I will be using in the interface table. |

|----------------------------------------|-------------------------------------------------------------------|

| Initial Doc Created 2/4/2022           | Filled out complete document as a draft for revision              |

# 4.2 Plasma Generation

### 4.2.1 Description

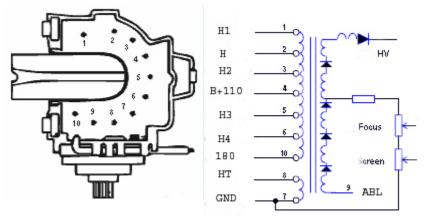

The Plasma Generation block consists of the transformer and electrodes used to amplify the voltage to create the electric arc. This is used to step up the voltage nearly 800 times for the electrodes. This block may also include large capacitors to speed up the circuit's transient response and provide instant voltage to the electrodes for the high-frequency sound signals.

### 4.2.2 Design

### Black Box Diagram:

### Schematic:

### 4.2.3 General Validation

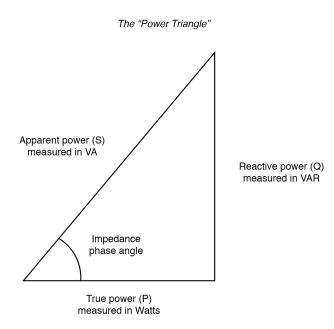

The transformer will be able to step up the voltage high enough for an electrical arc to be produced. To produce an electric arc, the transformer must output more than 75,000 volts for our expected one-inch gap between the electrodes. The input voltage needs to be high enough so that the transformer can produce the needed 75,000 volts.[1]

### 4.2.4 Interface Validation

| Interface Property | Why is this interface this value? | Why do you know that your design details for this block |

|--------------------|-----------------------------------|---------------------------------------------------------|

|                    |                                   | above meet or exceed each<br>property?                  |

#### otsd\_plsm\_gnrtn\_other : Input

| Other: Tubing<br>Specification: 1/2"<br>outer-diameter | This size of tubing allows for the right amount of helium to be present in the chamber. | The tubing specifications                                      |

|--------------------------------------------------------|-----------------------------------------------------------------------------------------|----------------------------------------------------------------|

| Other: Concentration:<br>80%                           | This will allow the right amount<br>of oxygen and helium so the arc<br>can be activated | The helium is constantly being pumped into the closed chamber. |

| Other: Tubing<br>Specification: 3/8"<br>inner-diameter | This size of tubing allows for the right amount of helium to be present in the chamber. | The tubing specifications                                      |

| Other: Type of Gas:<br>Helium | Helium allows for a lower resistance for the arc to bridge | We will have a tank of helium pumping into out chamber |

|-------------------------------|------------------------------------------------------------|--------------------------------------------------------|

#### pwr\_plsm\_gnrtn\_dcpwr : Input

| Inominal: 3 Amps | The nominal current power is able to produce | With high voltage this current will provide enough Power to the transformer to produce an arc.                                                                             |

|------------------|----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Ipeak: 4.5 Amps  | The peak current power is able to produce    | With high voltage this current will provide more than enough Power to the transformer to produce an arc.                                                                   |

| Vmax: 20 Volts   | The maximum Voltage power is able to produce | The transformer is able to step<br>up a voltage by 800 Therefor with<br>20 Volts the transformer will be<br>able to provide enough voltage to<br>produce an electric arc   |

| Vmin: 10.5 Volts | The minimum voltage power is able to produce | The transformer is able to step<br>up a voltage by 800 Therefor with<br>10.5 Volts the transformer will be<br>able to provide enough voltage to<br>produce an electric arc |

### hgh\_pwr\_swtchng\_\_plsm\_gnrtn\_acpwr : Input

| Inominal: 1A | The nominal current high power switching is able to produce | With high voltage this current will provide enough Power to the transformer to produce an arc.                                                                        |

|--------------|-------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Vmax: 40 VAC | The maximum Voltage high power switching is able to produce | The transformer is able to step<br>up a voltage by 800 Therefor with<br>40VAC the transformer will be<br>able to provide enough voltage to<br>produce an electric arc |

| Vmin: 24 VAC | The minimum voltage high power switching is able to produce | The transformer is able to step<br>up a voltage by 800 Therefor with<br>24VAC the transformer will be<br>able to provide enough voltage to<br>produce an electric arc |

#### plsm\_gnrtn\_otsd\_envout : Output

| Other: dBmin: 60 dB at<br>1 Meter     | Average dB for a conversion at<br>1 Meter[2]                                                                        | The high voltage charges the air<br>around it and the switching<br>current will expand and contract<br>the air creating a sound higher<br>than 60 dB. |

|---------------------------------------|---------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| Other: Voltage: 75,000<br>Volt min    | It takes 75,000 Volts for<br>electricity to jump an inch<br>distance [1]                                            | The transformer can be wound to produce a much higher voltage than this minimum.                                                                      |

| Other: Frequency: 20K<br>Hz to 35K Hz | To low of a frequency and the transformer doesn't work, to high of a frequency and not enough power to transformer. | Transformer needs switching<br>current to operate and boost the<br>voltage. The output frequency is<br>the same speed as the input<br>frequency.      |

#### 4.2.5 Verification Process

- 1. Plug transformer into high power switching block and power block

- 2. Set inputs from power block to 3 amps and 10.5 volts

- 3. Set Inomial to 3 amp

- 4. Set input voltage to 20 Vac

- 5. Test/Verify a range of 20 35K Hz

- 6. Verify that noise level is above 60 dB at 1 meter away

- 7. Show arc is present verifying at least 75,000 volt output

- 8. Set input to 7.8 Vac

- 9. Do steps 4 6 again.

- 10. Set inputs from power block to 4.5 amps and 20 volts

- 11. Do steps 3 9 again.

### 4.2.6 References and File Links

[1] K. Wallewein, "How many volts does it take for electricity to ... - quora," *Quora*, 2018. [Online]. Available:

https://www.quora.com/How-many-volts-does-it-take-for-electricity-to-jump-to-another-metal-obj ect. [Accessed: 07-Jan-2022].

### 4.2.7 Revisions Table

| Торіс                                  | Revision                                                                                                 |

|----------------------------------------|----------------------------------------------------------------------------------------------------------|

| Interface Properties - 3/4/22          | Updated interface properties to make block diagram update                                                |

| Verifican plan - 1/21/22               | Rewrote plan to test all possible input/output combinations.                                             |

| Schematic changed - 1/21/22            | Changed schematic to only represent my block.                                                            |

| Interface properties changed - 1/21/22 | Conversed with Don and my team to define testable outputs for my block and changed them in the table.    |

| Document Finalized - 1/7/22            | Added references, and reformatted documents.                                                             |

| Content Added - 1/5/22                 | Added content to Verification Plan, Interface<br>Validation, General Validation, and Design<br>Sections. |

| Initial Document Created - 1/5/22      | Copy and paste from the online tool.                                                                     |

# 4.3 Bluetooth

### 4.3.1 Description

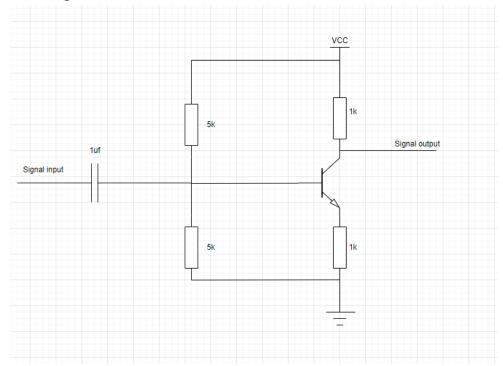

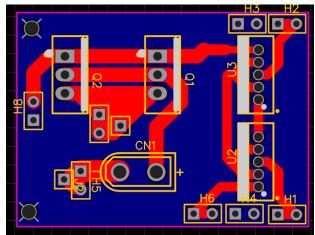

The Bluetooth receiving module includes a Bluetooth audio module and a bias circuit. The Bluetooth audio module uses A2DP protocol to communicate with external Bluetooth signals and decodes audio data to generate audio analog signals. The bias circuit then biases the audio signal to produce a bias signal consistent with the sampling of the post-stage ADC.

### 4.3.2 Design

Block diagram:

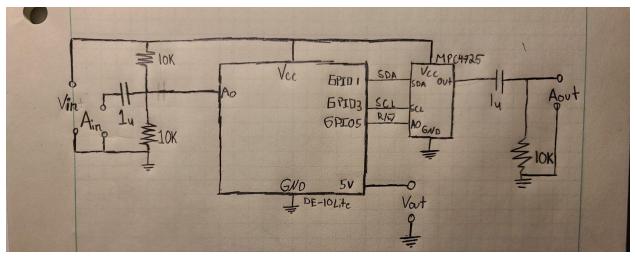

Schematic Diagram: Bias circuit

External Bluetooth signals are received by Bluetooth audio module, analyzed by on-chip protocol, decoded by audio, and finally output as analog signals through DAC. The bias circuit biases the generated analog signal and provides gain appropriately, so that the signal can maximize the coverage of sampling range, improve sampling accuracy.

### 4.3.3 General Validation

Verify that the Bluetooth audio module can be stably paired with external Bluetooth devices.

Verify that the Bluetooth audio module can send data according to the specified protocol and can decode it correctly

a bias circuit can add dc bias to the audio signal and provide appropriate gain The rear ADC sampling can correctly sample the analog signal output from the bias circuit.

#### 4.3.4 Interface Validation

| Interface Property | Why is this interface of this |

|--------------------|-------------------------------|

|                    | value?                        |

|                    |                               |

Why do you know that your design details <u>for this block</u> above meet or exceed each property?

#### otsd\_bltth\_rcvr\_\_rf

| External Bluetooth signal protocol | A2DP Protocol                                     | The module supports the universal Bluetooth audio protocol                                                                                                                                                                          |

|------------------------------------|---------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Host input source data format      | WAV/MP3                                           | Common audio formats that are resolvable by the module protocol                                                                                                                                                                     |

| Bias circuit signal output         | Vmin: 0V<br>Vmax: 5V<br>Imin: 0 mA<br>Imax: 10 mA | According to the data manual<br>of the rear stage module, the<br>input voltage range is<br>between 0V and 5V, and the<br>driving current is less than<br>10mA, which meets the<br>electrical requirements of the<br>rear DAC driver |

The Bluetooth audio module can receive an external Bluetooth signal and generate an analog signal.

The bias circuit provides the correct bias and amplifies the signal appropriately.

#### 4.3.5 Verification Process

- 1. External devices can be paired with Bluetooth audio modules

- 2. The Bluetooth audio module relates to a small speaker to play music normally

3. Measure the output waveform amplitude of the bias circuit within the input range of the rear ADC

- 4. Test bias circuit with standard source can provide bias and gain normally

- 5. Joint adjustment with the post-stage signal processing unit

### 4.3.6 References and File Links

Data sheet about Bluetooth receiver:

https://www.amazon.com/MakerHawk-Bluetooth-Receiver-Amplifier-Speaker/dp/B08D94PGCG/ ref=sxin\_14\_ac\_d\_bv?ac\_md=0-0-QmVzdCBWYWx1ZQ%3D%3D-ac\_d\_bv\_bv\_bv&crid=GKJT R9OP03VL&cv\_ct\_cx=bluetooth%2Bchip&keywords=bluetooth%2Bchip&pd\_rd\_i=B08D94PGC G&pd\_rd\_r=92eb7a4e-fb36-422f-b9f3-c0a4efb74fa5&pd\_rd\_w=WhDwn&pd\_rd\_wg=DFMXV&pf \_rd\_p=148e9898-1bed-4a70-9840-46f32e4185bd&pf\_rd\_r=JPJ5CPRRDQRFWCN8FSN1&qid= 1641618998&sprefix=bluetooth%2Bchi%27p%2Caps%2C152&sr=1-1-f4ff053e-b1e8-4d31-8f95 -56d755c862ba&th=1

### 4.3.7 Revisions Table

| Date      | Торіс               | Revision                                                                     |

|-----------|---------------------|------------------------------------------------------------------------------|

| 2022/1/20 | Reword some details | Re-do block diagram, and rewrite interface validation and verification plan. |

## 4.4 Waveform Generation Modulation

#### 4.4.1 Description

Taking the analog audio signal as an input, the WGM block will modify the duty cycle of a square wave. This modulation is what implants the audio within the eventual high-power signal. The modulated square wave is then split into a buffer and an inverter to create mirrored signals perfectly in phase. This is used to create the push-pull characteristics needed to sustain high voltage. This will be implemented with 3 different integrated circuits, one for pulse width modulation, one buffer, and one inverter.

### 4.4.2 Design

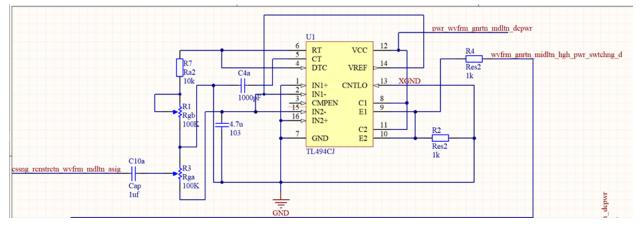

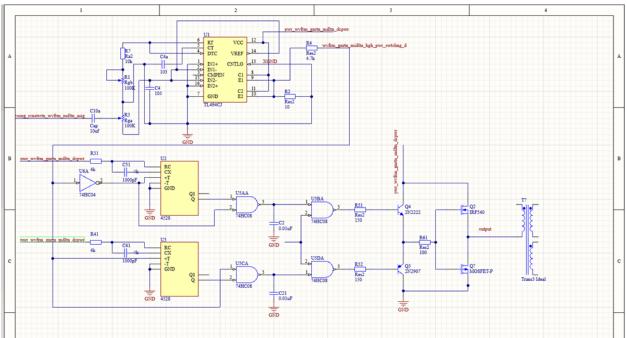

The WGM module is depicted above, and the upper left port is a DC input module with a 5V supply voltage to power the circuit. And the left bottom port is a signal following signal preprocessing; audio frequency modulation is accomplished by continually modifying the duty ratio of the PWM wave; and the right port is an output modulated square wave. Through a buffer and an inverter, the modulated PWM wave generates a mirror image signal with the same phase. The two output signals combine to generate a push-pull circuit that powers the IRFP260N. The innovation has the advantages of high output power and low heat generation while maintaining the push-out characteristic required by high voltage, and it can respond fast to the driving signal, allowing for a good restoration of the audio signal.

## 4.4.3 General Validation

The module binds the pre-processed audio to the TL494's fourth pin via a capacitor and then modifies the fourth pin's voltage to affect the pulse width, so altering the temperature of the ion body and generating sound. The module employs a MOS single tube driving mode; the thirteenth pin of the TL494 is grounded, namely, the 12th pin is at a low level, and the output waveforms of the two triodes in the TL494 are consistent, allowing for control of the PWM waveform produced by the MOS hard switch's output modulation.

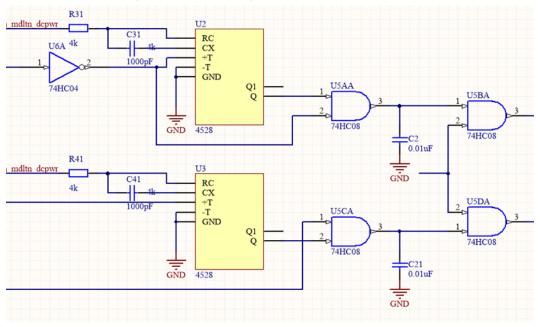

## 4.4.3.2 Inverting and buffering module

The inversion module is based on the 74HC04 logic element, while the buffer module is based on the CC4528, which has the purpose of preventing the microswitch from shaking and

delaying, as well as efficiently triggering the MOS tube. and after passing through the 74HC04, outputting two lines of mirror image PWM waveforms to be used as driving signals for the MOS tubes in the circuit.

#### 4.4.3.3 Drive Circuit

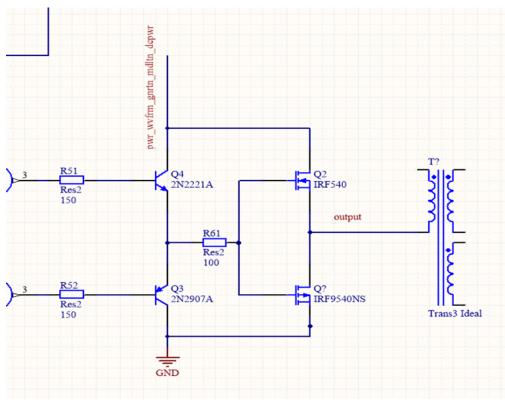

As illustrated in the figure above, the inverse buffer module's control signal has a high output voltage and a low current, necessitating the use of a MOS tube with a low GS capacitance to minimize damage to the MOS tube and triode. Two triodes are used in the module circuit to drive the N-type MOS and the P-type MOS, forming a GS capacitor discharge circuit that accelerates the MOS turning-off while minimizing switching loss.

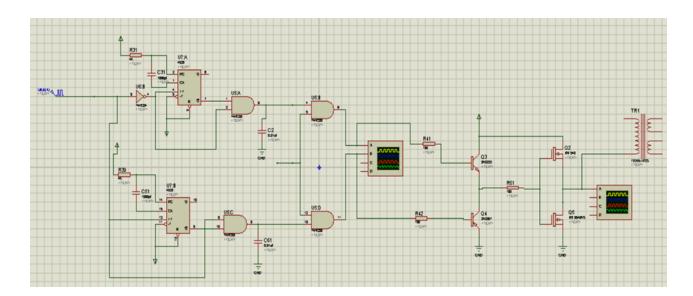

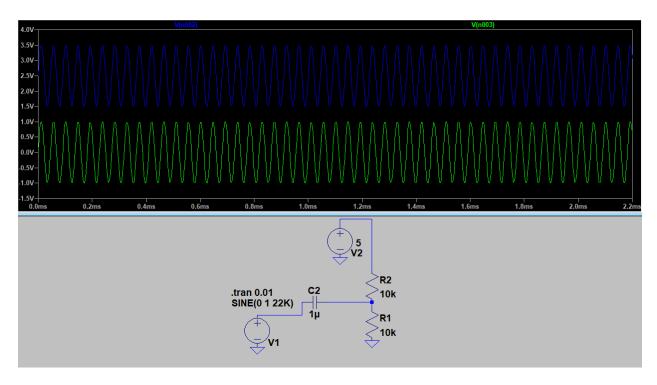

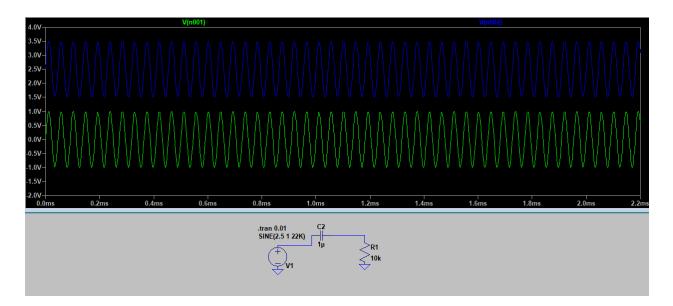

The PWM inverter, buffer and drive circuits are verified by protues software. A simulation circuit is established as follows:

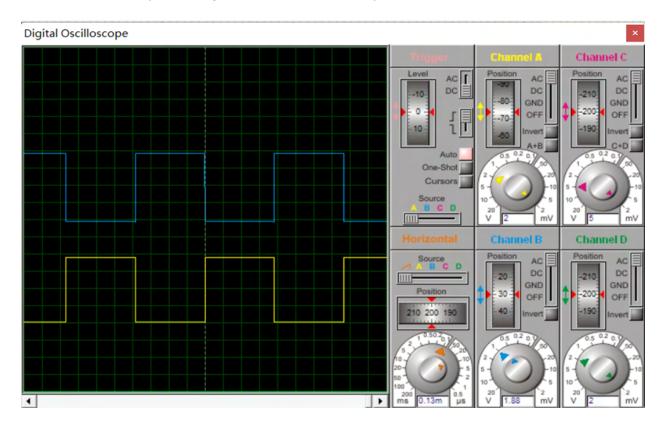

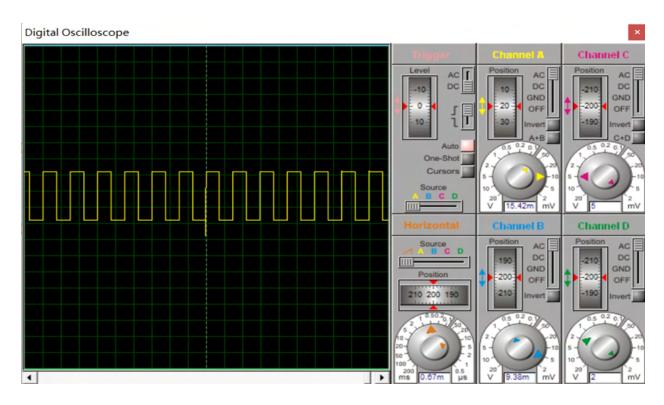

The above test circuit accepts a PWM signal and simulates an audio waveform modulated by the TL494. The output of one path is inverted and delayed, while the output of the second path is buffered and delayed driving Q3 and Q4, respectively.

The above figure shows the two output waveforms after inversion and buffering, and it can be seen from the figure that the output is a mirror PWM waveform, which meets the expected design requirements.

The above diagram shows the PWM waveform generated when the MOS is turned off after the MOS transistor is driven to operate, and the output is sent to the transformer.

## 4.4.3.4 Whole Circuit

## 4.4.4 Interface Validation

#### pwr\_wvfrm\_gnrtn\_mdltn\_dcpwr : Input

| Ipeak: 2 Amps | the components in this block.  | In the circuit, I designed a sliding<br>rheostat, which can adjust different<br>currents according to different<br>voltages, so 2A is feasible. |

|---------------|--------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| Vmax: 5 Volts | provided enough power to work. | The circuit can pass the voltage of<br>5V, through the sliding rheostat<br>adjustment, can realize the<br>corresponding current                 |

#### sgnl\_prcssng\_rcnstrctn\_wvfrm\_gnrtn\_mdltn\_asig : Input

| Max Frequency: 20K<br>Hz | hearing | PWM is a modulation module that<br>can be adjustable at 100KHZ, so<br>20K Hz can be realized. |

|--------------------------|---------|-----------------------------------------------------------------------------------------------|

| Vmax: 1.5V               | · · ·   | According to the test, the circuit satisfies this input                                       |

| Vrange: +-1V             |         | According to the test, the circuit satisfies this input                                       |

#### wvfrm\_gnrtn\_mdltn\_hgh\_pwr\_swtchng\_\_dsig : Output

| Logic-Level: 10V | TL494 PWM control chipset is used After multimeter testing, the circuit |

|------------------|-------------------------------------------------------------------------|

|                  | to create the PWM signal that can output this value and can drive       |

|                  | drives the gate of the MOSFET and the MOSFET gates.                     |

|                  | the switching action. The datasheet                                     |

|                  | lists the maximum collector output                                      |

|                  | voltage (output signal) as 41V.                                         |

|                  | Thus, 10V falls easily below this                                       |

|                  | and within spec for the chipset.                                        |

|                  |                                                                         |

| Other: Fmin=8KHz  |                                 | Use oscilloscope, according to the tests, square waves can be generated at this output       |

|-------------------|---------------------------------|----------------------------------------------------------------------------------------------|

| Other: Fmax=25KHz | frequency is because the square | Use oscilloscope, according to the<br>tests, square waves can be<br>generated at this output |

#### 4.4.5 Verification Process

1. Use multimeter, test the circuit, when the current is 2A, what is the voltage

2. Test the circuit, when the voltage is 5V, what is the current

3. Test whether 20KHz can work when PWM is connected to signal processing module, and test Vmax and Vrange

4. When the circuit is connected to the power supply, test whether the output is 10V

5. Use oscilloscope, test the waveform, when the minimum frequency is 8KHz and the maximum frequency is 25KHz, whether the square wave can be realized

### 4.4.6 References and File Links

IRFP260N MOSFET Datasheet - link

TL494 PWM Control Chipset Datasheet - link

#### 74HC04 logic elements:

https://www.digikey.com/htmldatasheets/production/2095793/0/0/1/74hc-t-04.html?utm\_adgroup =xGeneral&utm\_source=google&utm\_medium=cpc&utm\_campaign=Dynamic%20Search\_EN\_ Product&utm\_term=&utm\_content=xGeneral&gclid=Cj0KCQiApL2QBhC8ARIsAGMm-KFnXfet WD-pyaLK1-bqlz118TPv0usLSbcQiVzuh9RybzMxyJFQnnAaAvvrEALw\_wcB

CD4528 buffer Datasheet: https://www.futurlec.com/4000Series/CD4528.shtml

## 4.4.7 Revisions Table

| Date      | Торіс         | Revision                                                                                         |

|-----------|---------------|--------------------------------------------------------------------------------------------------|

| 2022/2/4  | Initial Draft | Initial Draft by Zhenglun Yang and will<br>update some details after circuit design<br>completed |

| 2022/2/18 | Second Draft  | Add circuit diagram and schematic, add some info.                                                |

# 4.5 High Power Switching

## 4.5.1 Description

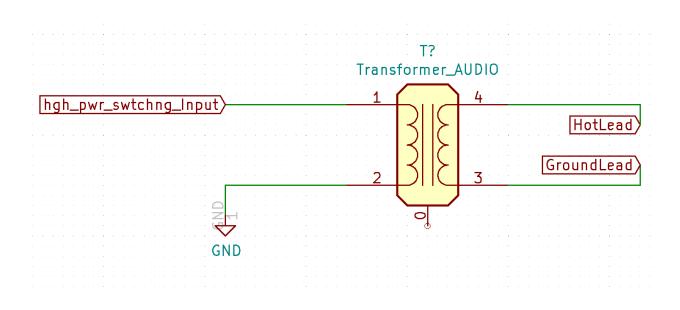

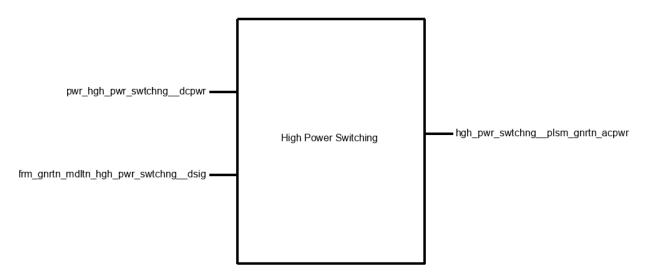

The outputs from the Waveform Generation and Modulation block are not capable of providing enough power to the transformer to create the electrical arc. Thus those signals are instead fed into the High Power Switching block which steps up the PWM signal to a higher voltage using a power MOSFET. This higher voltage signal is then inputted into the transformer, creating enough voltage to initiate the electrical arc. The High Power Switching block requires high voltage DC power from the system's Power Block in order to drive the MOSFET. The high power switching uses a single n-channel MOSFET as a low-side driver to sink current down through the transformers primary coil. This provides a single ended (single direction) high voltage and high current signal to the transformer. Additional protection and filtering components are necessary to support the MOSFET as well as heatsinks and careful thermal considerations.

## 4.5.2 Design

Figure 4.5.1: High Power Switching Black Box Diagram

Figure 1 above shows the black box diagram for the High Power Switching block. The *pwr\_hgh\_pwr\_swtchng\_dcpwr* input is the DC power input that supplies power to the MOSFET. The *frm\_gntn\_mdltn\_hgh\_pwr\_swtchng\_dsign* input is the PWM input from the Waveform Generation and Modulation Block that encodes the audio signal for the speaker. The *hgh\_pwr\_swtchng\_plsm\_gnrtn\_acpwr* output is the amplified PWM output signal that gets sent through the primary winding of the transformer. This output signal gets stepped up again by the transformer in the Plasma Generation block and directly creates the plasma arc for the speaker.

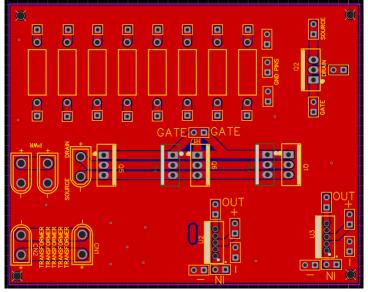

Figure 4.5.2: High Power Switching Schematic with System

Figure 2 above shows the High Power Switching block outlined in red. The block is shown with the transformer for better clarity of system flow. The final design of the block converged to a single low-side NMOS MOSFET driver to pull current through the transformer. A high voltage power rail is connected to the high side of the primary coil in the transformer, and thus the drain of the MOSFET. The 12V PWM input signal is connected to the gate of the MOSFET, switching the device on and off. When the input signal is high, the Vgs threshold voltage of the MOSFET is exceeded and the device switches to the triode region of operation and conducts the current through the transformer to ground. When the PWM is low, the Vgs threshold for the device is not exceeded and it acts as an open circuit, thus not allowing any current to flow through the transformer.

A low-side design was selected instead of a high-side design (PMOS transistor above the transformer, with source connected directly to the supply) due to the nature of the PWM input signal. If a PMOS high-side MOSFET was used, the gate voltage would need to be higher to best control the Vov of the MOSFET because the Vgs is referenced off the supply voltage.

The 1000hm resistor on the MOSFET gate is to reduce parasitic oscillations that occur due to the MOSFETs input capacitance combined with the input circuitry's inductance. This slows down the turn-on time of the MOSFET and causes excess current to flow through the drain/source impedance.

MOSFET: IRFP260N

Resistor: 1000hm, 5W

### 4.5.3 General Validation

#### 3.1 MOSFET Verification

The power FET for the block was selected based on voltage and current ratings as well as timing and thermal properties. Calculations done with the transformer and voltage requirements/impedances for electrical arcing showed that the MOSFET needed to create a voltage between 24 and 40V. Thus the maximum Vds tolerance of the transistor needed to be well above this to work most efficiently. Along with the high supply voltage, switching transformers often cause voltage spikes due to the inductive nature of their coils. A voltage rating of >100V was desirable. The IRFP260N MOSFET has a Vds voltage rating of 200V, giving plenty of headroom.

The Ids current tolerance of the MOSFET was also important. Although the actual current through the MOSFET while in use is highly dependent on the transformer load, a very high 5A peak current was identified. The IRFP260N MOSFET has a continuous Idc current rating of 50A at 10V Vgs, again giving plenty of headroom.

The next main requirement for the MOSFET was switching speed. Our speaker system is set to use a frequency less than a maximum of 50KHz, thus the MOSFET would have to support this.

Simple math shows that the maximum allowed total switching time for the MOSFET would be 20microseconds. This includes turn-on delay, rise time, turn-off delay, and fall time. Table 1 below shows the timing specs from the IRFP260N MOSFET datasheet. The total switching time is calculated to be 180ns or 0.18microseconds. Thus allowing for the MOSFET to switch at an ideal 5.5GHz. Even considering parasitics that would cut this nearly in half, the MOSFET still gives plenty of headroom for our application.

| t <sub>d(on)</sub>  | Turn-On Delay Time  | <br>17 |        | V <sub>DD</sub> = 100V  |

|---------------------|---------------------|--------|--------|-------------------------|

| t <sub>r</sub>      | Rise Time           | <br>60 | <br>ne | I <sub>D</sub> = 28A    |

| t <sub>d(off)</sub> | Turn-Off Delay Time | <br>55 | <br>ns | $R_G = 1.8\Omega$       |

| t <sub>f</sub>      | Fall Time           | <br>48 |        | V <sub>GS</sub> = 10V ④ |

| Table 4.5.1: IRFP260N | Timing Specs |

|-----------------------|--------------|

|-----------------------|--------------|

The last main requirement for the MOSFET is the thermal and power requirement. The main contributor to MOSFET thermal issues is the drain/source impedance which burns power when the device is switching between on and off. The equation to estimate this power dissipation for a switching MOSFET is as follows:

PDSWITCHING = (CRSS × VIN<sup>2</sup> × fSW × ILOAD)/IGATE

Plugging in values from the IRFP260N datasheet and nominal output/input currents and voltages at 50Khz gives a value of 5.29Watts of power dissipation. The IRFP260N is rated to 300W, with a linear derating factor of 2 W/degreeC. Thus even as the device heats up, the power dissipation will reach nowhere near the maximum rated value.

Other important aspects of the MOSFET for our application are the Vgs tolerances and the diode protection. The IRFP260N has a maximum Vgs voltage of 20V, giving our 12V PWM input signal a significant amount of headroom. The IRFP260N MOSFET also includes a convenient body diode shown as a protection measure against reverse current.

In conclusion, the IRFP260N MOSFET exceeds all of the necessary requirements and was chosen for the design.

The chosen single MOSFET design leads to much easier testing and construction of the circuit as well as a simplified process of sourcing components. With only one MOSFET acting as a switch, the circuit can be constructed for testing on a protoboard or even wired together. This leads to faster turnarounds for testing and allows the team to further design and test the rest of the system. Along with this, any errors or problems that do occur can easily be troubleshooted due to simple signal flow through the circuit. While a single MOSFET design is less technically astounding, the time saved on sourcing, testing, and constructing the circuit will be put to better use in other aspects of the system design, leading to a more refined final product. Component availability is also restricted as specific high power MOSFETs are available only online, with an average of 2-week shipping time. The selected IRFP260N MOSFET is already on hand and ready to be tested.

## 4.5.4 Interface Validation

| Interface Property | Why is this interface this | Why do you know that your            |

|--------------------|----------------------------|--------------------------------------|

|                    | value?                     | design details <u>for this block</u> |

|                    |                            | above meet or exceed each            |

|                    |                            | property?                            |

## pwr\_hgh\_pwr\_swtchng\_\_dcpwr : Input

| Inominal: 1 Amp | 1A DC at the Vmin of 24V gives<br>24W of power, and gives 40W of<br>power at the Vmax of 40V. Using<br>the known 1:800 ratio of the<br>flyback transformer and the<br>transformer output voltages<br>calculated below, this leads to a<br>transformer output current of<br>1.25mA at both Vmin and Vmax.<br>This is above the current<br>threshold for both output voltages<br>to produce an electrical arc of the<br>desired length. Electrical arcs are<br>produced mainly due to high<br>voltage potential differences, thus<br>the current values do not need to<br>be high. | This current gets sunk through the<br>drain of the MOSFET. The<br>IRFP260N MOSFET has a<br>continuous current rating of 50A at<br>25C, and 35A at 100C. The<br>datasheet also lists the maximum<br>pulsed drain current at 200A. Thus<br>even at high temperature, 1A of<br>current is far below the maximum<br>threshold for the device. |